# Elements of Power Electronics

## PART I: Bases

Fabrice Frébel (fabrice.frebel@uliege.be)

September 15<sup>th</sup>, 2025

# Goal and expectations

The goal of the course is to provide a toolbox that allows you to:

- ▶ understand power electronics concepts and topologies,

- ▶ to model a switching converter,

- ▶ to build it (including its magnetic components) and,

- ▶ to control it (with digital control).

Power Electronics is a huge area and the correct approach is to focus on **understanding** concepts.

# Organization and material

The course is divided in three parts:

- ▶ PART I: Bases

- ▶ PART II: Digital control

- ▶ PART III: Topologies and applications

In PART I and PART III, chapters are numbered according to the reference book [1].

In PART II, chapters are numbered according to the reference book [2].

# PART I: Bases

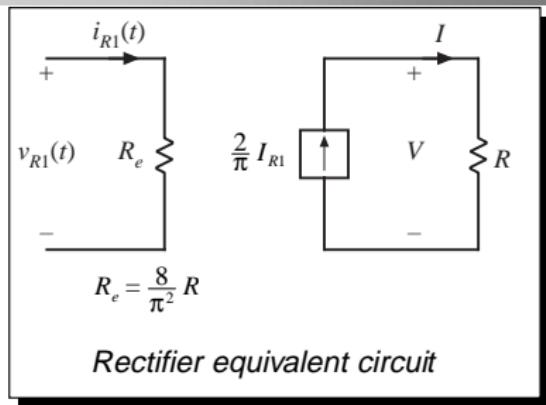

- ▶ Chapter 1: Introduction

- ▶ Chapter 2: Principles of Steady-State Converter Analysis

- ▶ Chapter 3: Steady-State Equivalent Circuit Modeling, Losses, and Efficiency

- ▶ Chapter 4: Switch Realization

- ▶ Chapter 5: The Discontinuous Conduction Mode

- ▶ Chapter 13: Basic Magnetics Theory

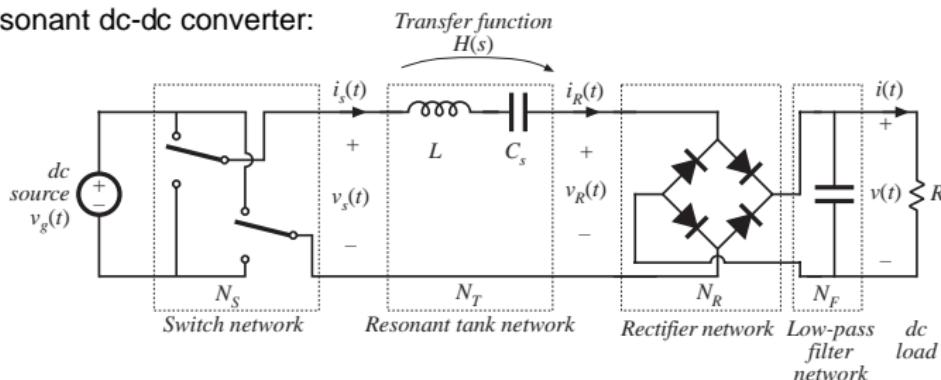

- ▶ Chapter 19: Resonant Converters

# Chapter 1: Introduction

---

---

# Fundamentals of Power Electronics

## Second edition

Robert W. Erickson

Dragan Maksimovic

University of Colorado, Boulder

# 1.1 Introduction to Power Processing

*Dc-dc conversion:*

Change and control voltage magnitude

*Ac-dc rectification:*

Possibly control dc voltage, ac current

*Dc-ac inversion:*

Produce sinusoid of controllable magnitude and frequency

*Ac-ac cycloconversion:* Change and control voltage magnitude and frequency

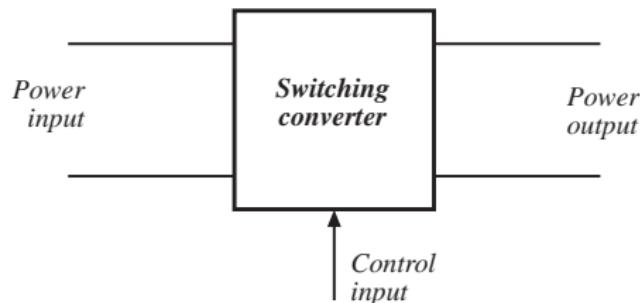

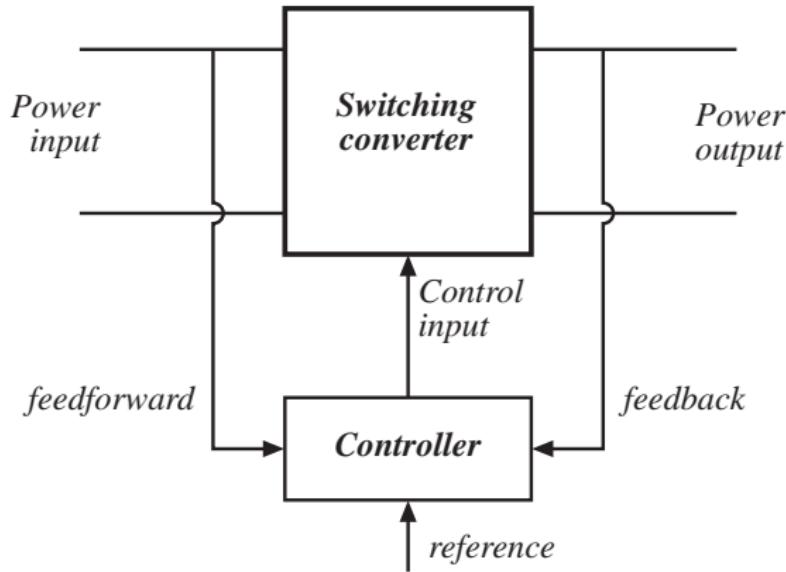

# Control is invariably required

# High efficiency is essential

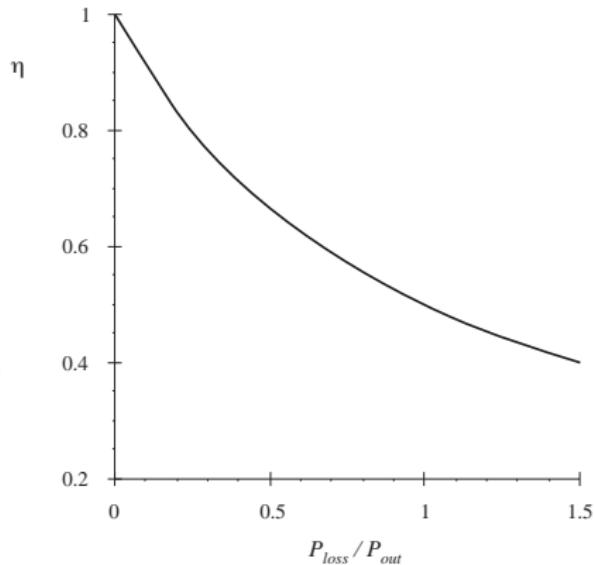

$$\eta = \frac{P_{out}}{P_{in}}$$

$$P_{loss} = P_{in} - P_{out} = P_{out} \left( \frac{1}{\eta} - 1 \right)$$

High efficiency leads to low power loss within converter

Small size and reliable operation is then feasible

Efficiency is a good measure of converter performance

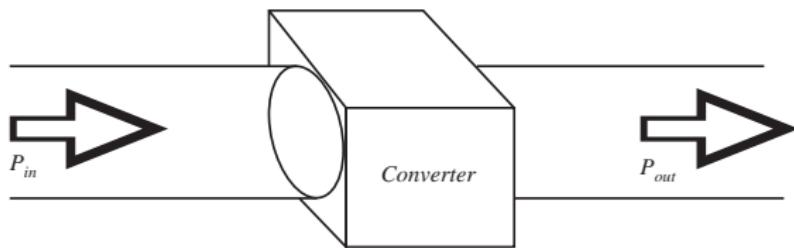

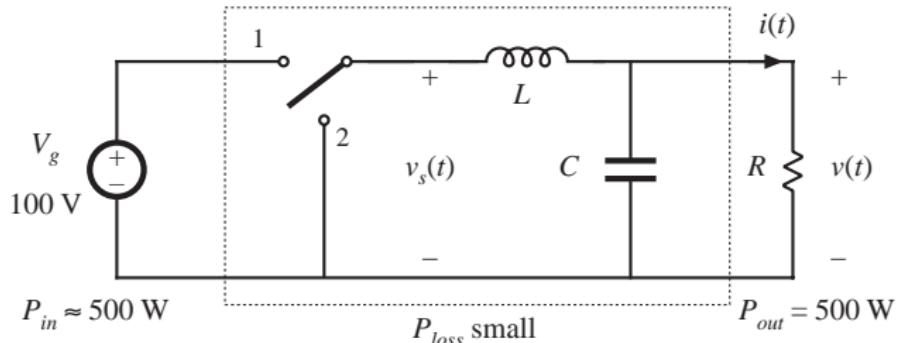

# A high-efficiency converter

---

A goal of current converter technology is to construct converters of small size and weight, which process substantial power at high efficiency

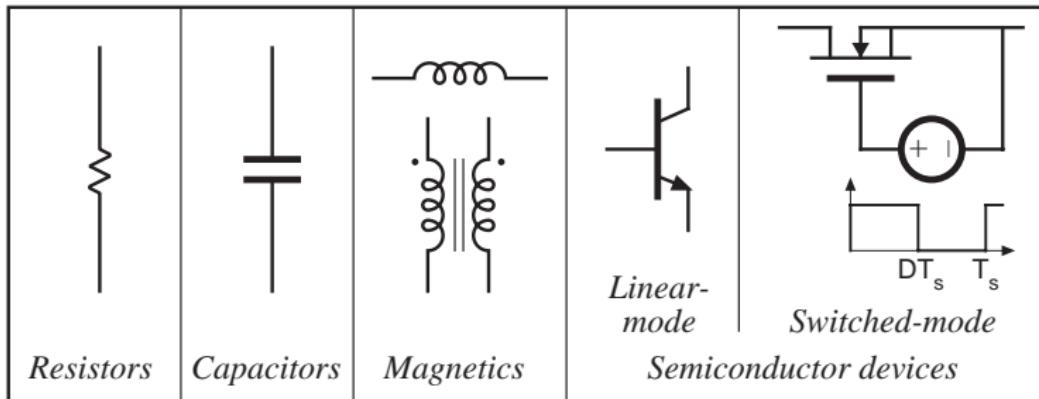

# Devices available to the circuit designer

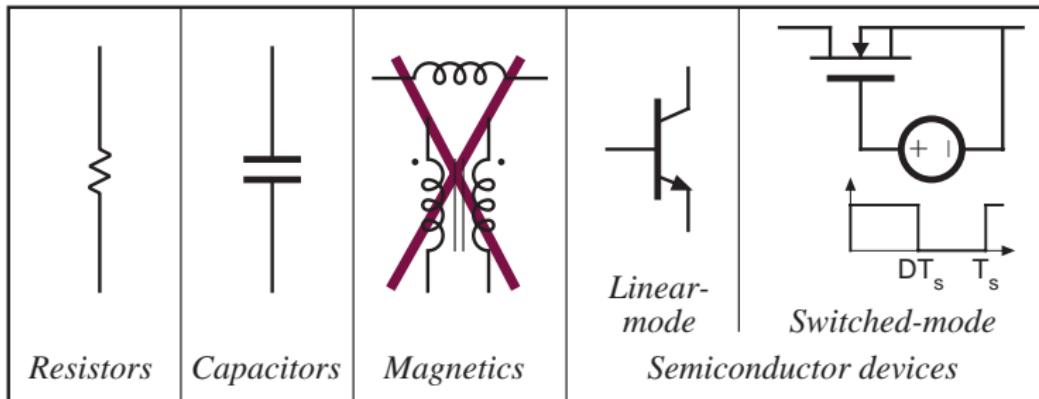

# Devices available to the circuit designer

Signal processing: avoid magnetics

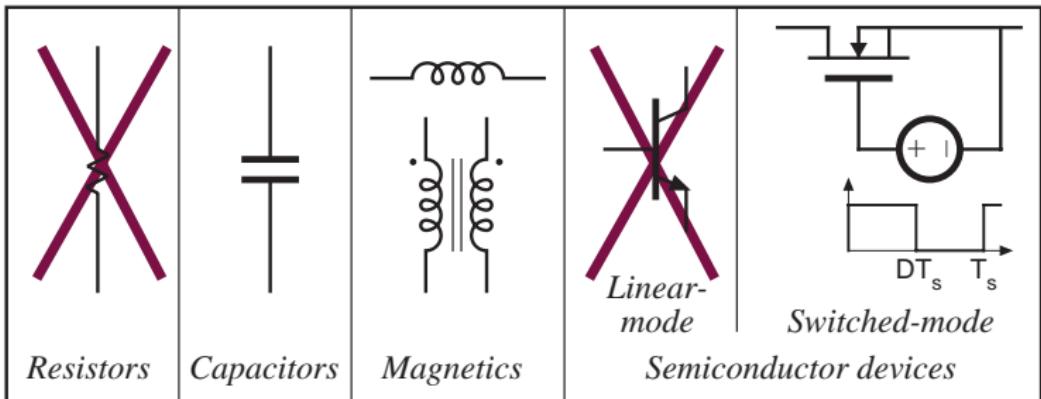

# Devices available to the circuit designer

Power processing: avoid lossy elements

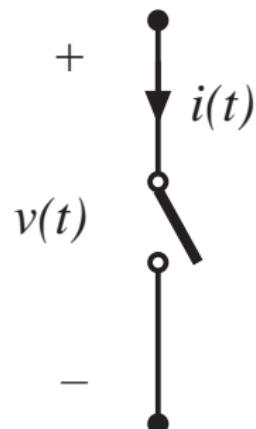

# Power loss in an ideal switch

---

Switch closed:  $v(t) = 0$

Switch open:  $i(t) = 0$

In either event:  $p(t) = v(t) i(t) = 0$

Ideal switch consumes zero power

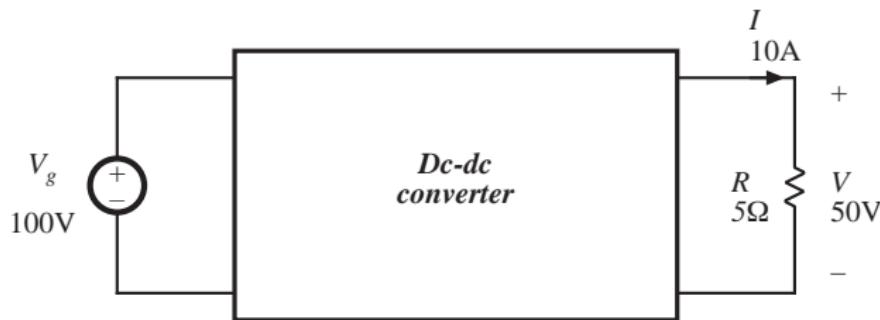

# A simple dc-dc converter example

Input source: 100V

Output load: 50V, 10A, 500W

How can this converter be realized?

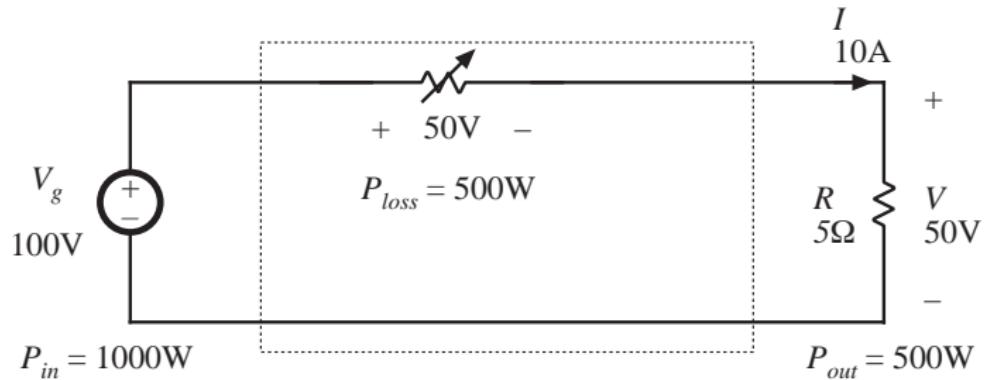

# Dissipative realization

## Resistive voltage divider

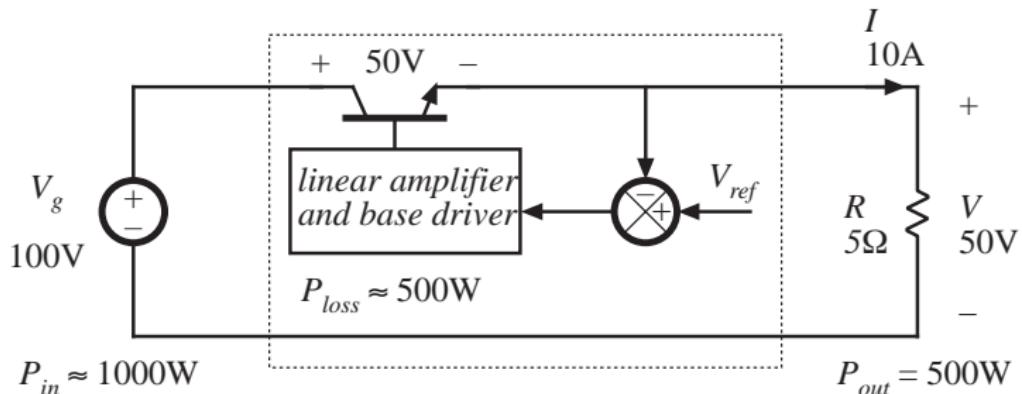

# Dissipative realization

Series pass regulator: transistor operates in active region

# Solutions?

- ▶ Can we find a better (more efficient) solution than the resistive voltage divider?

- ▶ What can we do to increase the voltage ( $V > V_g$ )?

- ▶ How can we create a galvanic isolation between the source and the load?

We will answer these questions in the following chapters.

## 1.2 Several applications of power electronics

---

Power levels encountered in high-efficiency converters

- less than 1 W in battery-operated portable equipment

- tens, hundreds, or thousands of watts in power supplies for computers or office equipment

- kW to MW in variable-speed motor drives

- 1000 MW in rectifiers and inverters for utility dc transmission lines

- ▶ 2.1 Introduction

- ▶ 2.2 Inductor volt-second balance, capacitor charge balance, and the small ripple approximation

- ▶ 2.3 Boost converter example

- ▶ 2.4 Cuk converter example

- ▶ 2.5 Estimating the ripple in converters containing two-pole low-pass filters

- ▶ Addendum: Inductor volt-second balance, capacitor charge balance, the fast way

- ▶ 2.6 Summary of key points

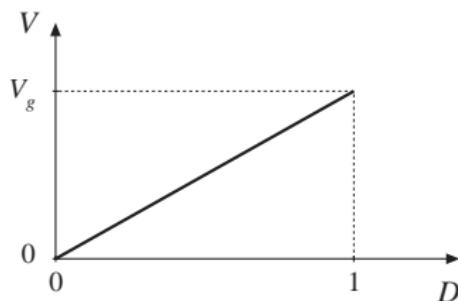

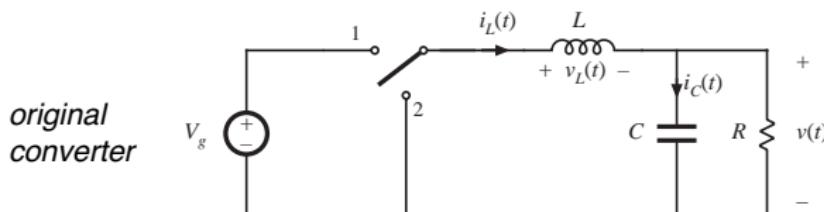

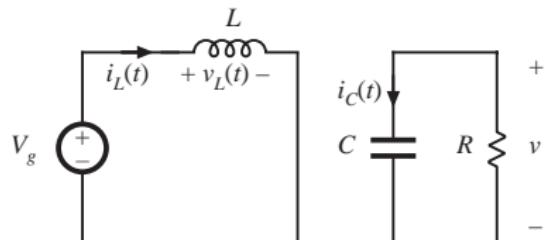

## 2.1 Introduction Buck converter

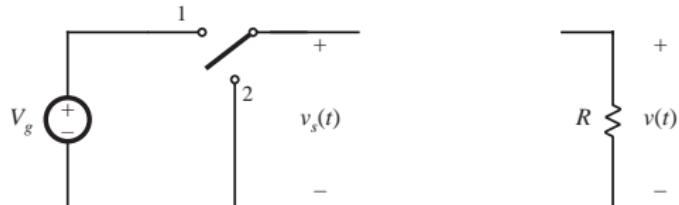

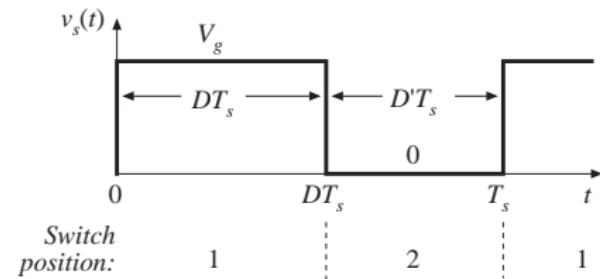

*SPDT switch changes dc component*

*Switch output voltage waveform*

Duty cycle  $D$ :

$0 \leq D \leq 1$

complement  $D'$ :

$D' = 1 - D$

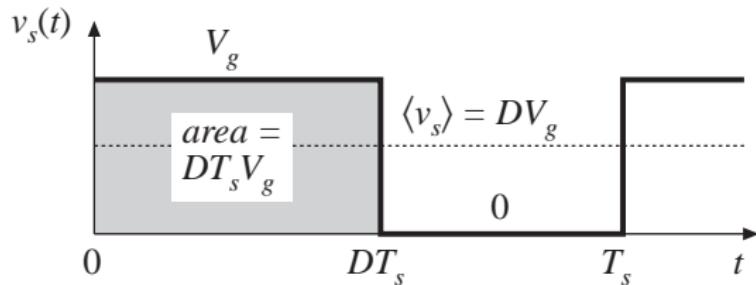

## Dc component of switch output voltage

*Fourier analysis: Dc component = average value*

$$\langle v_s \rangle = \frac{1}{T_s} \int_0^{T_s} v_s(t) dt$$

$$\langle v_s \rangle = \frac{1}{T_s} (DT_s V_g) = DV_g$$

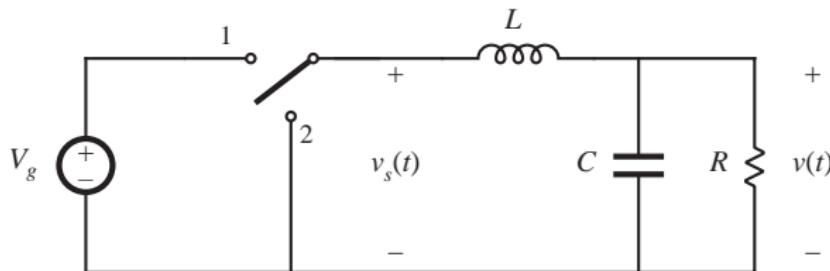

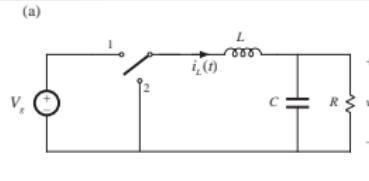

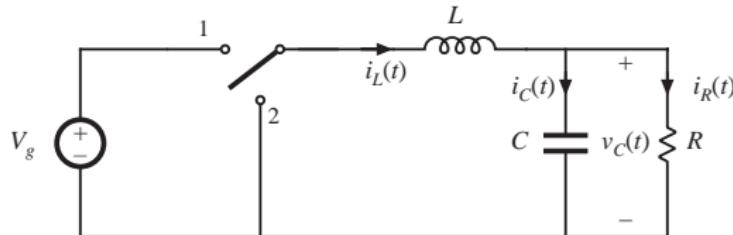

# Addition of low pass filter

Addition of (ideally lossless)  $L$ - $C$  low-pass filter, for removal of switching harmonics:

- Choose filter cutoff frequency  $f_0$  much smaller than switching frequency  $f_s$

- This circuit is known as the “buck converter”

## Insertion of low-pass filter to remove switching harmonics and pass only dc component

$$v \approx \langle v_s \rangle = DV_g$$

# Three basic dc-dc converters

*Buck*

*Boost*

*Buck-boost*

# Objectives of this chapter

---

- Develop techniques for easily determining output voltage of an arbitrary converter circuit

- Derive the principles of *inductor volt-second balance* and *capacitor charge (amp-second) balance*

- Introduce the key *small ripple approximation*

- Develop simple methods for selecting filter element values

- Illustrate via examples

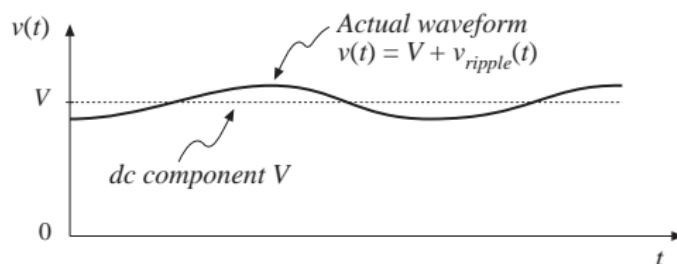

## 2.2. Inductor volt-second balance, capacitor charge balance, and the small ripple approximation

Actual output voltage waveform, buck converter

*Buck converter

containing practical

low-pass filter*

*Actual output voltage

waveform*

$$v(t) = V + v_{\text{ripple}}(t)$$

# The small ripple approximation

In a well-designed converter, the output voltage ripple is small. Hence, the waveforms can be easily determined by ignoring the ripple:

$$\| v_{\text{ripple}} \| \ll V$$

$$v(t) \approx V$$

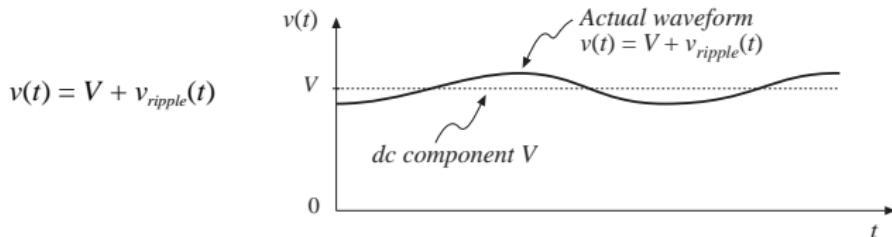

# Buck converter analysis: inductor current waveform

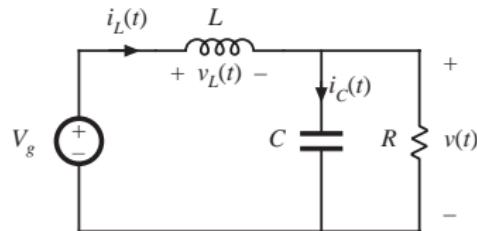

# Inductor voltage and current

## Subinterval 1: switch in position 1

*Inductor voltage*

$$v_L = V_g - v(t)$$

*Small ripple approximation:*

$$v_L \approx V_g - V$$

*Knowing the inductor voltage, we can now find the inductor current via*

$$v_L(t) = L \frac{di_L(t)}{dt}$$

*Solve for the slope:*

$$\frac{di_L(t)}{dt} = \frac{v_L(t)}{L} \approx \frac{V_g - V}{L}$$

$\Rightarrow$  *The inductor current changes with an essentially constant slope*

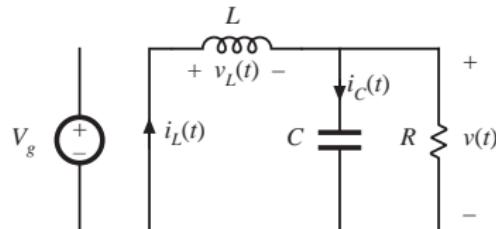

# Inductor voltage and current

## Subinterval 2: switch in position 2

*Inductor voltage*

$$v_L(t) = -v(t)$$

*Small ripple approximation:*

$$v_L(t) \approx -V$$

*Knowing the inductor voltage, we can again find the inductor current via*

$$v_L(t) = L \frac{di_L(t)}{dt}$$

*Solve for the slope:*

$$\frac{di_L(t)}{dt} \approx -\frac{V}{L}$$

$\Rightarrow$  *The inductor current changes with an essentially constant slope*

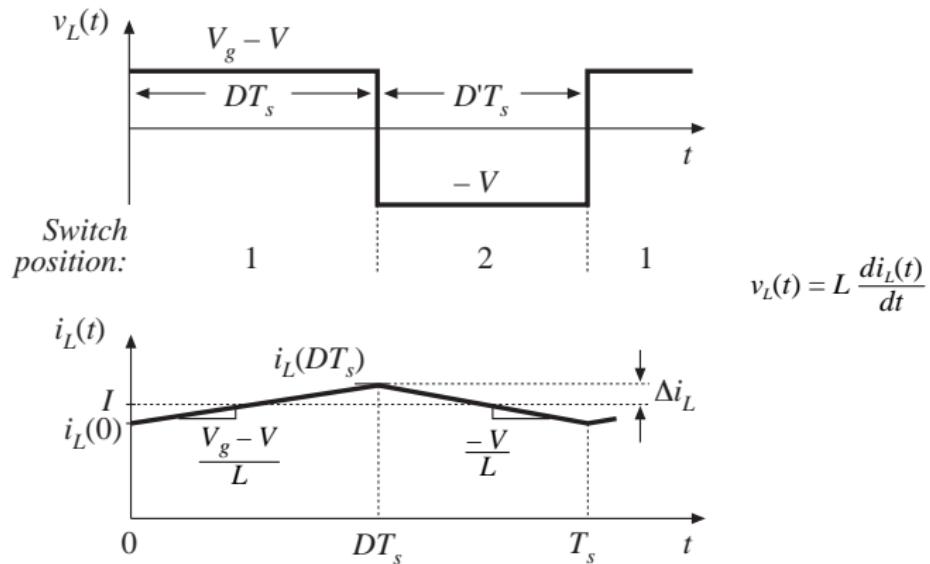

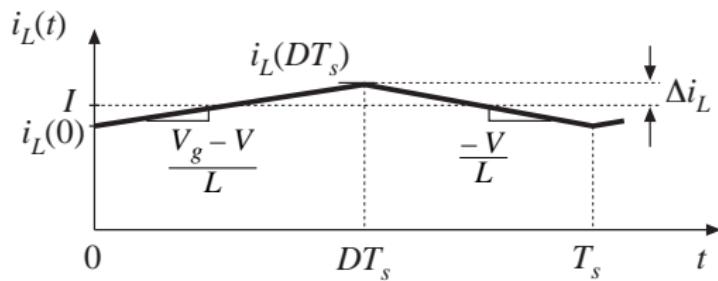

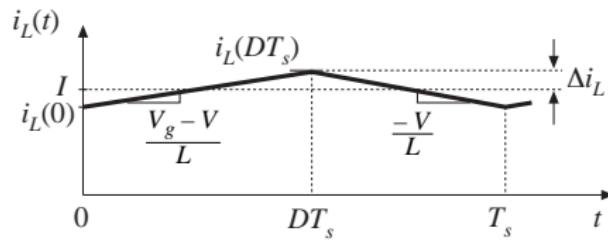

# Inductor voltage and current waveforms

# Determination of inductor current ripple magnitude

$(\text{change in } i_L) = (\text{slope})(\text{length of subinterval})$

$$(2\Delta i_L) = \left( \frac{V_g - V}{L} \right) (DT_s)$$

$$\Rightarrow \Delta i_L = \frac{V_g - V}{2L} DT_s \quad L = \frac{V_g - V}{2\Delta i_L} DT_s$$

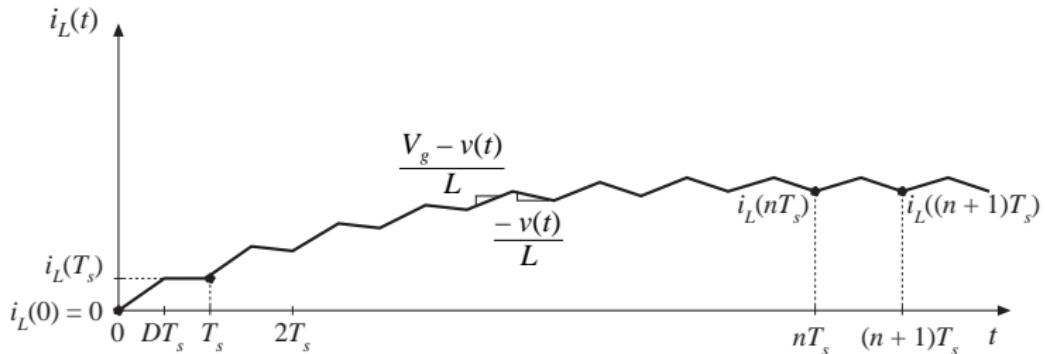

# Inductor current waveform during turn-on transient

When the converter operates in equilibrium:

$$i_L((n+1)T_s) = i_L(nT_s)$$

# The principle of inductor volt-second balance: Derivation

---

Inductor defining relation:

$$v_L(t) = L \frac{di_L(t)}{dt}$$

Integrate over one complete switching period:

$$i_L(T_s) - i_L(0) = \frac{1}{L} \int_0^{T_s} v_L(t) dt$$

In periodic steady state, the net change in inductor current is zero:

$$0 = \int_0^{T_s} v_L(t) dt$$

*Hence, the total area (or volt-seconds) under the inductor voltage waveform is zero whenever the converter operates in steady state.*

An equivalent form:

$$0 = \frac{1}{T_s} \int_0^{T_s} v_L(t) dt = \langle v_L \rangle$$

*The average inductor voltage is zero in steady state.*

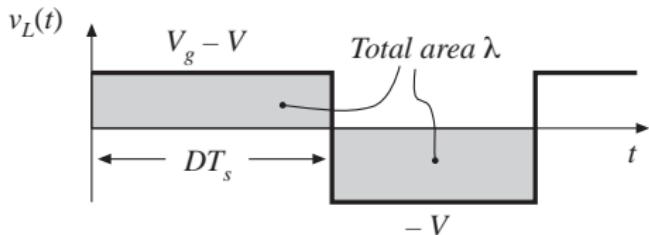

# Inductor volt-second balance: Buck converter example

*Inductor voltage waveform,

previously derived:*

Integral of voltage waveform is area of rectangles:

$$\lambda = \int_0^{T_s} v_L(t) dt = (V_g - V)(DT_s) + (-V)(D'T_s)$$

Average voltage is

$$\langle v_L \rangle = \frac{\lambda}{T_s} = D(V_g - V) + D'(-V)$$

Equate to zero and solve for  $V$ :

$$0 = DV_g - (D + D')V = DV_g - V \quad \Rightarrow \quad V = DV_g$$

# The principle of capacitor charge balance: Derivation

---

Capacitor defining relation:

$$i_c(t) = C \frac{dv_c(t)}{dt}$$

Integrate over one complete switching period:

$$v_c(T_s) - v_c(0) = \frac{1}{C} \int_0^{T_s} i_c(t) dt$$

In periodic steady state, the net change in capacitor voltage is zero:

$$0 = \frac{1}{T_s} \int_0^{T_s} i_c(t) dt = \langle i_c \rangle$$

*Hence, the total area (or charge) under the capacitor current waveform is zero whenever the converter operates in steady state. The average capacitor current is then zero.*

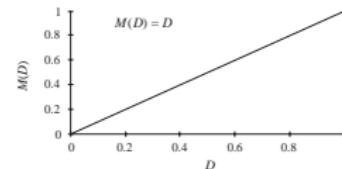

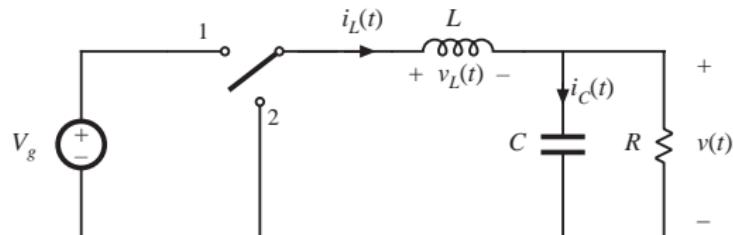

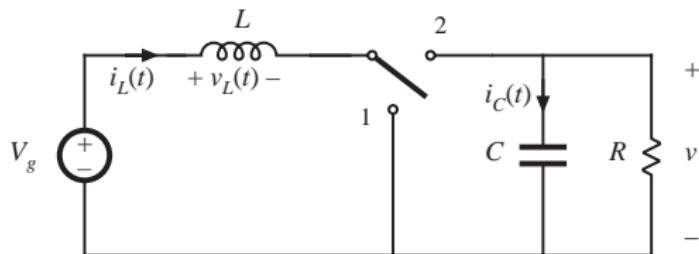

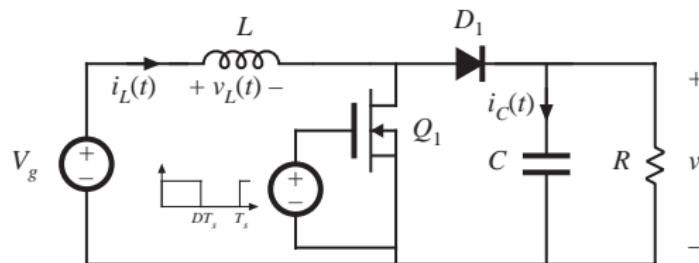

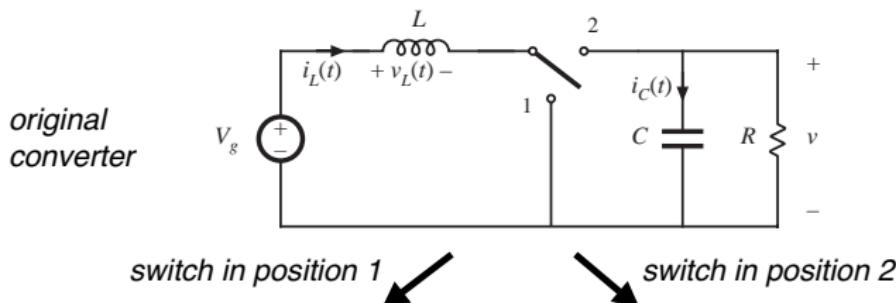

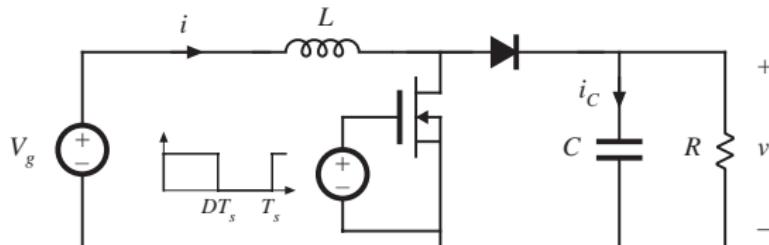

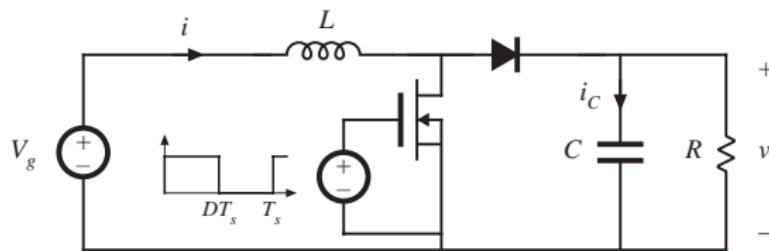

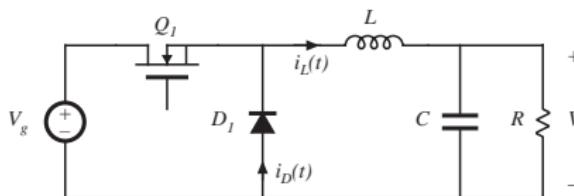

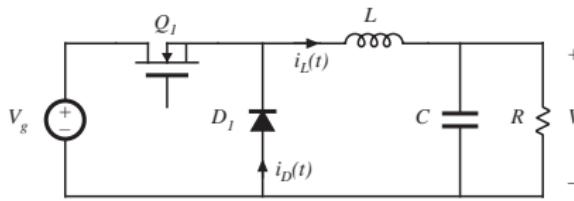

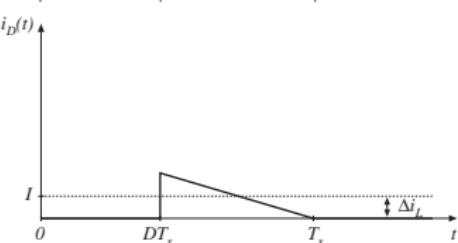

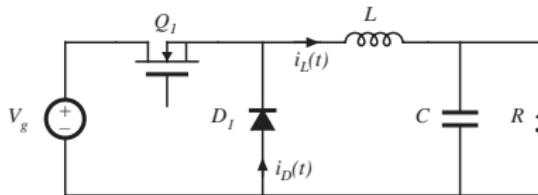

## 2.3 Boost converter example

*Boost converter

with ideal switch*

*Realization using

power MOSFET

and diode*

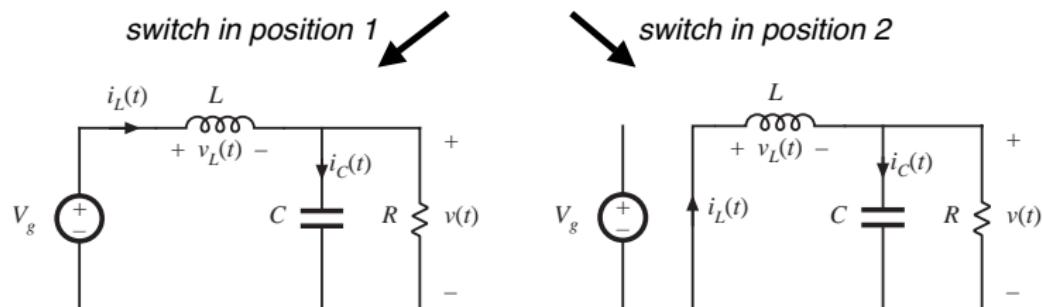

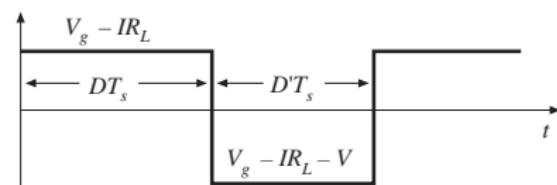

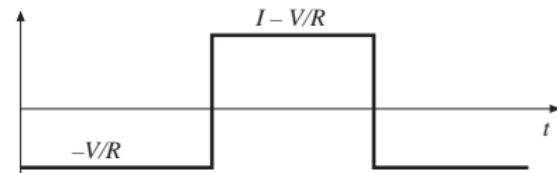

# Boost converter analysis

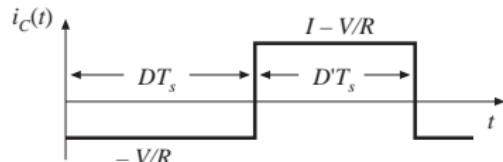

# Subinterval 1: switch in position 1

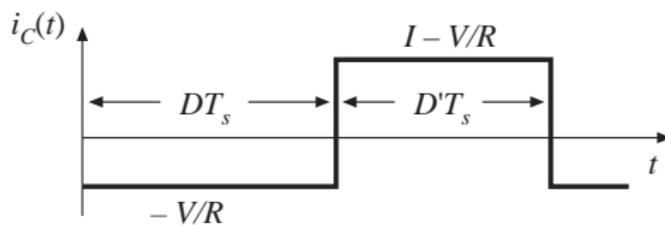

*Inductor voltage and capacitor current*

$$v_L = V_g$$

$$i_C = -v / R$$

*Small ripple approximation:*

$$v_L = V_g$$

$$i_C = -V / R$$

## Subinterval 2: switch in position 2

*Inductor voltage and capacitor current*

$$v_L = V_g - v$$

$$i_C = i_L - v / R$$

*Small ripple approximation:*

$$v_L = V_g - V$$

$$i_C = I - V / R$$

# Inductor voltage and capacitor current waveforms

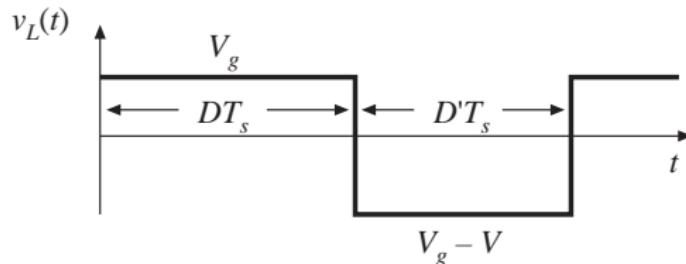

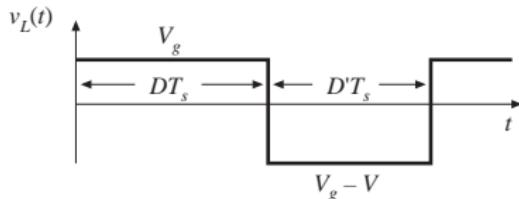

# Inductor volt-second balance

Net volt-seconds applied to inductor over one switching period:

$$\int_0^{T_s} v_L(t) dt = (V_g) DT_s + (V_g - V) D'T_s$$

Equate to zero and collect terms:

$$V_g (D + D') - V D' = 0$$

Solve for V:

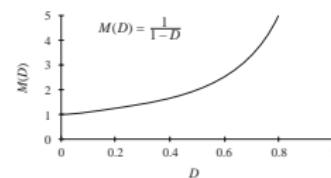

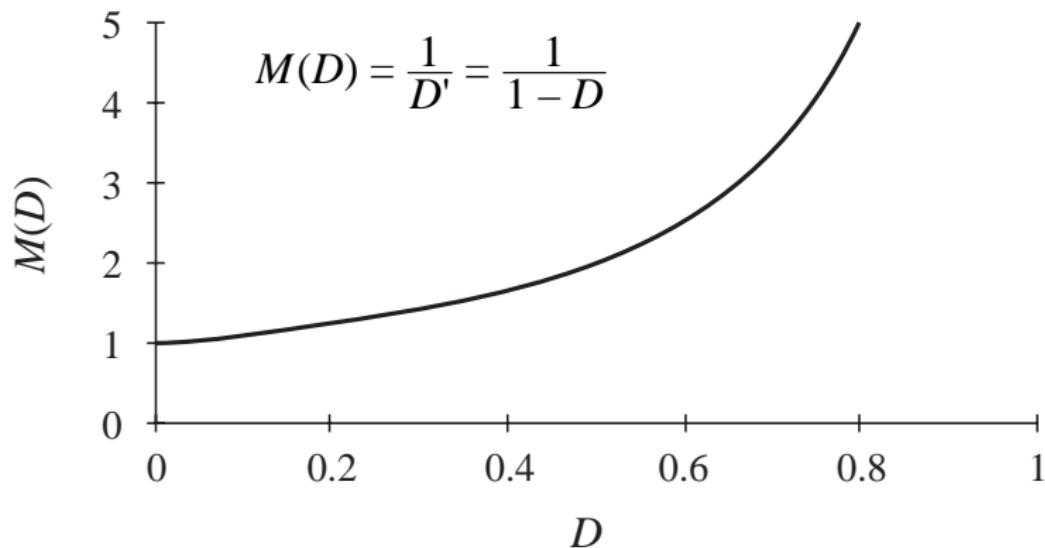

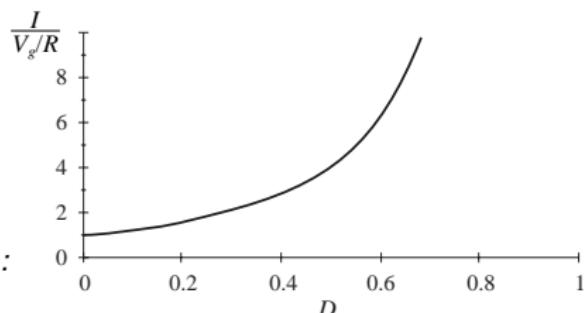

$$V = \frac{V_g}{D'}$$

The voltage conversion ratio is therefore

$$M(D) = \frac{V}{V_g} = \frac{1}{D'} = \frac{1}{1 - D}$$

## Conversion ratio $M(D)$ of the boost converter

# Determination of inductor current dc component

Capacitor charge balance:

$$\int_0^{T_s} i_C(t) dt = \left(-\frac{V}{R}\right) DT_s + \left(I - \frac{V}{R}\right) D'T_s$$

Collect terms and equate to zero:

$$-\frac{V}{R} (D + D') + I D' = 0$$

Solve for  $I$ :

$$I = \frac{V}{D'R}$$

Eliminate  $V$  to express in terms of  $V_g$ :

$$I = \frac{V_g}{D'^2 R}$$

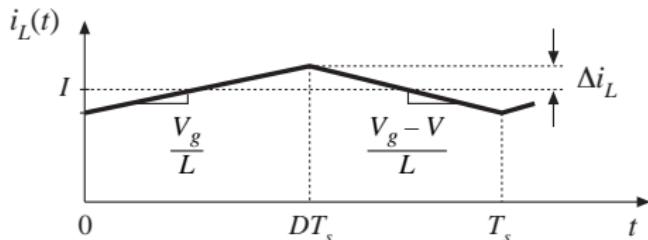

# Determination of inductor current ripple

Inductor current slope during subinterval 1:

$$\frac{di_L(t)}{dt} = \frac{v_L(t)}{L} = \frac{V_g}{L}$$

Inductor current slope during subinterval 2:

$$\frac{di_L(t)}{dt} = \frac{v_L(t)}{L} = \frac{V_g - V}{L}$$

Change in inductor current during subinterval 1 is (slope) (length of subinterval):

$$2\Delta i_L = \frac{V_g}{L} DT_s$$

Solve for peak ripple:

$$\Delta i_L = \frac{V_g}{2L} DT_s$$

- Choose  $L$  such that desired ripple magnitude is obtained

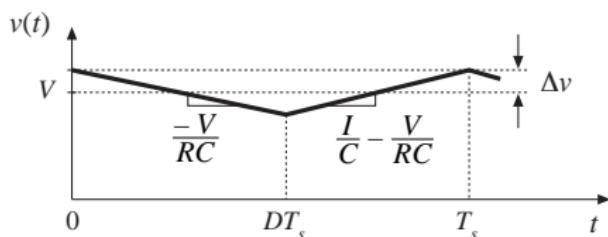

# Determination of capacitor voltage ripple

Capacitor voltage slope during subinterval 1:

$$\frac{dv_c(t)}{dt} = \frac{i_c(t)}{C} = -\frac{V}{RC}$$

Capacitor voltage slope during subinterval 2:

$$\frac{dv_c(t)}{dt} = \frac{i_c(t)}{C} = \frac{I}{C} - \frac{V}{RC}$$

Change in capacitor voltage during subinterval 1 is (slope) (length of subinterval):

$$-2\Delta v = -\frac{V}{RC} DT_s$$

Solve for peak ripple:

$$\Delta v = \frac{V}{2RC} DT_s$$

- Choose  $C$  such that desired voltage ripple magnitude is obtained

- In practice, capacitor *equivalent series resistance* (esr) leads to increased voltage ripple

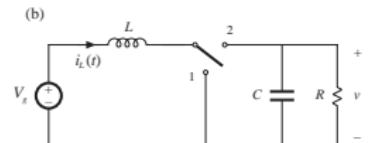

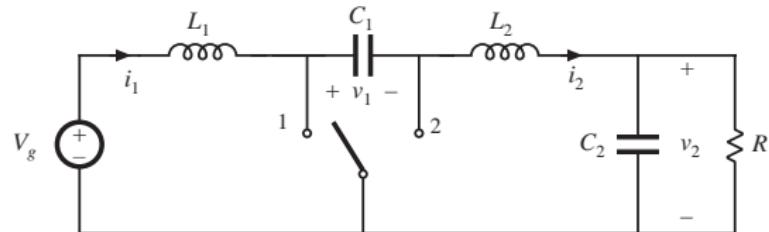

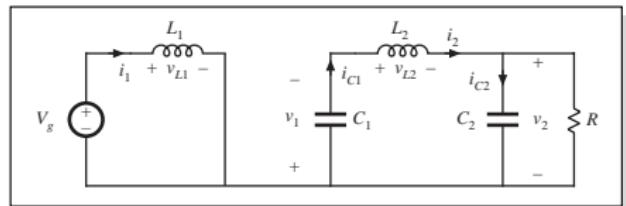

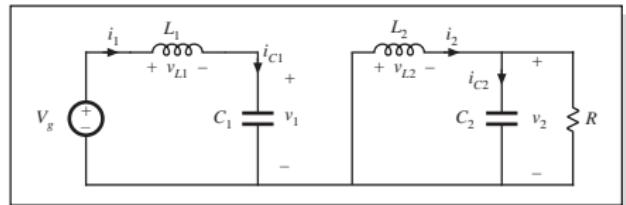

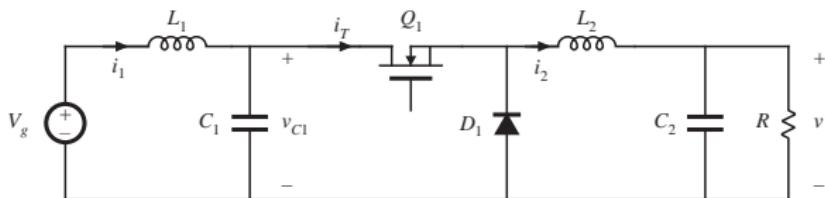

## 2.4 Cuk converter example

*Cuk converter,

with ideal switch*

*Cuk converter:

practical realization

using MOSFET and

diode*

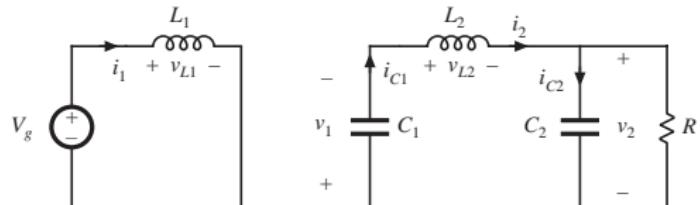

# Cuk converter circuit with switch in positions 1 and 2

Switch in position 1:

MOSFET conducts

Capacitor  $C_1$  releases

energy to output

Switch in position 2:

diode conducts

Capacitor  $C_1$  is

charged from input

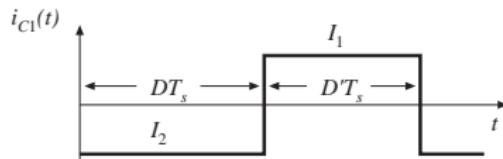

# Waveforms during subinterval 1

## MOSFET conduction interval

Inductor voltages and capacitor currents:

$$v_{L1} = V_g$$

$$v_{L2} = -v_1 - v_2$$

$$i_{C1} = i_2$$

$$i_{C2} = i_2 - \frac{v_2}{R}$$

Small ripple approximation for subinterval 1:

$$v_{L1} = V_g$$

$$v_{L2} = -V_1 - V_2$$

$$i_{C1} = I_2$$

$$i_{C2} = I_2 - \frac{V_2}{R}$$

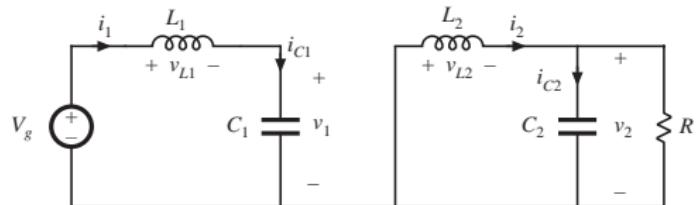

# Waveforms during subinterval 2

## Diode conduction interval

Inductor voltages and capacitor currents:

$$v_{L1} = V_g - v_1$$

$$v_{L2} = -v_2$$

$$i_{C1} = i_1$$

$$i_{C2} = i_2 - \frac{v_2}{R}$$

Small ripple approximation for subinterval 2:

$$v_{L1} = V_g - V_1$$

$$v_{L2} = -V_2$$

$$i_{C1} = I_1$$

$$i_{C2} = I_2 - \frac{V_2}{R}$$

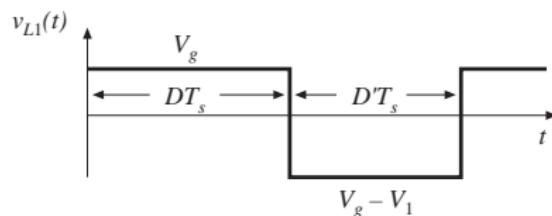

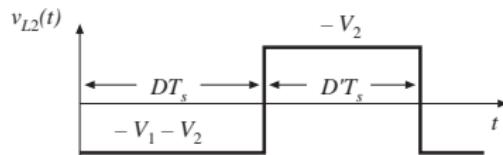

# Equate average values to zero

The principles of inductor volt-second and capacitor charge balance state that the average values of the periodic inductor voltage and capacitor current waveforms are zero, when the converter operates in steady state. Hence, to determine the steady-state conditions in the converter, let us sketch the inductor voltage and capacitor current waveforms, and equate their average values to zero.

## Waveforms:

Inductor voltage  $v_{L1}(t)$

Volt-second balance on  $L_1$ :

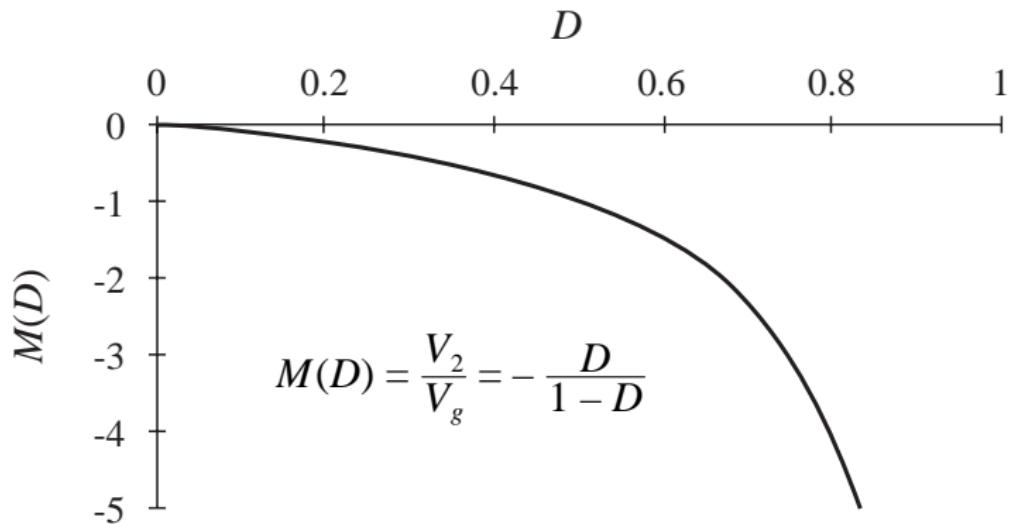

$$\langle v_{L1} \rangle = DV_g + D'(V_g - V_1) = 0$$

# Equate average values to zero

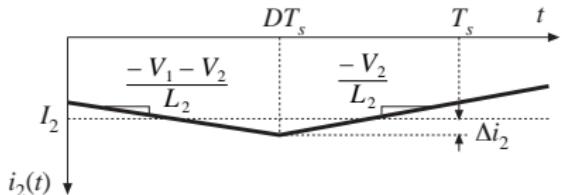

*Inductor  $L_2$  voltage*

Average the waveforms:

*Capacitor  $C_1$  current*

$$\langle v_{L2} \rangle = D(-V_1 - V_2) + D'(-V_2) = 0$$

$$\langle i_{C1} \rangle = DI_2 + D'I_1 = 0$$

# Equate average values to zero

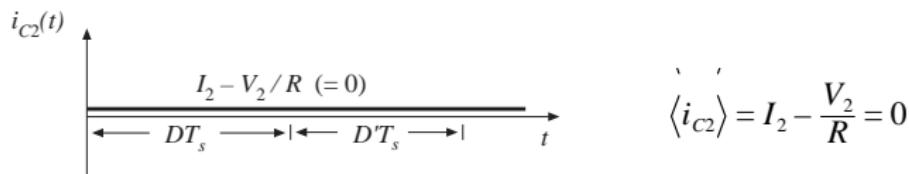

Capacitor current  $i_{C2}(t)$  waveform

Note: during both subintervals, the capacitor current  $i_{C2}$  is equal to the difference between the inductor current  $i_2$  and the load current  $V_2/R$ . When ripple is neglected,  $i_{C2}$  is constant and equal to zero.

# Cuk converter conversion ratio $M = V/V_g$

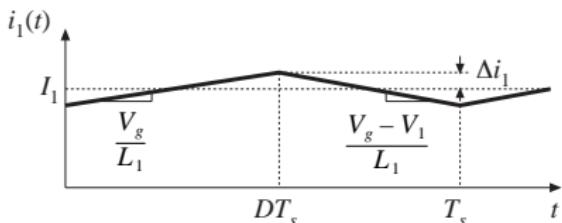

# Inductor current waveforms

Interval 1 slopes, using small ripple approximation:

$$\frac{di_1(t)}{dt} = \frac{v_{L1}(t)}{L_1} = \frac{V_g}{L_1}$$

$$\frac{di_2(t)}{dt} = \frac{v_{L2}(t)}{L_2} = \frac{-V_1 - V_2}{L_2}$$

Interval 2 slopes:

$$\frac{di_1(t)}{dt} = \frac{v_{L1}(t)}{L_1} = \frac{V_g - V_1}{L_1}$$

$$\frac{di_2(t)}{dt} = \frac{v_{L2}(t)}{L_2} = \frac{-V_2}{L_2}$$

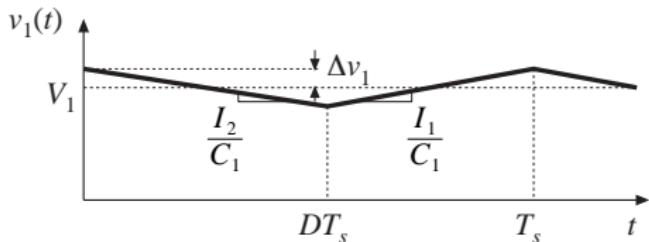

# Capacitor $C_1$ waveform

Subinterval 1:

$$\frac{dv_1(t)}{dt} = \frac{i_{C1}(t)}{C_1} = \frac{I_2}{C_1}$$

Subinterval 2:

$$\frac{dv_1(t)}{dt} = \frac{i_{C1}(t)}{C_1} = \frac{I_1}{C_1}$$

# Ripple magnitudes

---

Analysis results

$$\Delta i_1 = \frac{V_g DT_s}{2L_1}$$

$$\Delta i_2 = \frac{V_1 + V_2}{2L_2} DT_s$$

$$\Delta v_1 = \frac{-I_2 DT_s}{2C_1}$$

Use dc converter solution to simplify:

$$\Delta i_1 = \frac{V_g DT_s}{2L_1}$$

$$\Delta i_2 = \frac{V_g DT_s}{2L_2}$$

$$\Delta v_1 = \frac{V_g D^2 T_s}{2D'RC_1}$$

**Q:** How large is the output voltage ripple?

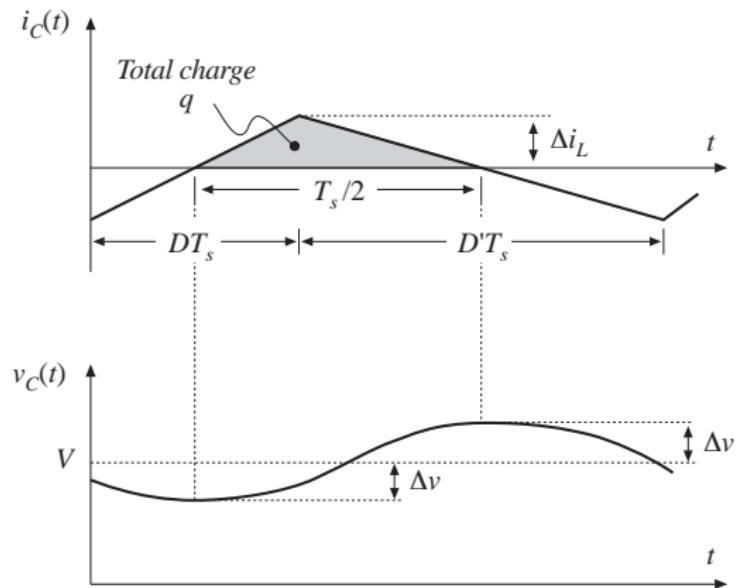

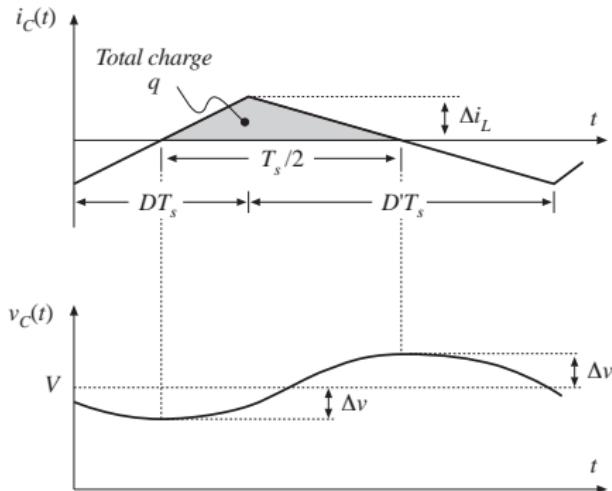

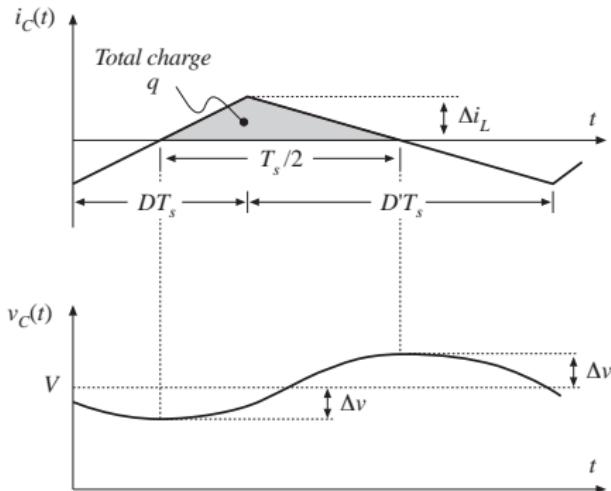

## 2.5 Estimating ripple in converters containing two-pole low-pass filters

*Buck converter example: Determine output voltage ripple*

*Inductor current waveform.*

*What is the capacitor current?*

# Capacitor current and voltage, buck example

*Must not

neglect

inductor

current ripple!*

*If the capacitor voltage ripple is small, then essentially all of the ac component of inductor current flows through the capacitor.*

# Estimating capacitor voltage ripple $\Delta v$

Current  $i_C(t)$  is positive for half of the switching period. This positive current causes the capacitor voltage  $v_C(t)$  to increase between its minimum and maximum extrema. During this time, the total charge  $q$  is deposited on the capacitor plates, where

$$q = C (2\Delta v)$$

$$(change \text{ in } charge) = C (change \text{ in } voltage)$$

# Estimating capacitor voltage ripple $\Delta v$

The total charge  $q$  is the area of the triangle, as shown:

$$q = \frac{1}{2} \Delta i_L \frac{T_s}{2}$$

Eliminate  $q$  and solve for  $\Delta v$ :

$$\Delta v = \frac{\Delta i_L T_s}{8 C}$$

Note: in practice, capacitor equivalent series resistance (esr) further increases  $\Delta v$ .

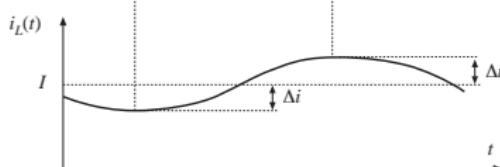

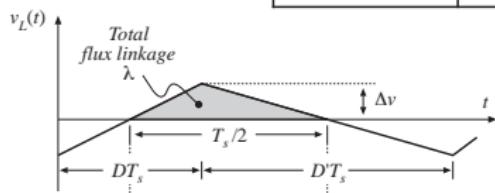

# Inductor current ripple in two-pole filters

Example:

problem 2.9

can use similar arguments, with

$\lambda = L (2\Delta i)$

$\lambda$  = inductor flux linkages

= inductor volt-seconds

# Inductor volt-second balance, capacitor charge balance, the fast way

The inductor volt-second balance and capacitor charge balance can be applied systematically as previously explained yielding to several equations to be solved. By inspecting the circuit it is possible to deduce some relationship in a faster way.

Note: the underlying inductor volt-second balance and capacitor charge balance principles are still applied.

- ▶ Replace inductors by short-circuits to deduce average voltages across capacitors.

- ▶ Replace capacitors by open-circuits to deduce average inductors and switches currents.

Example: CUK converter

## 2.6 Summary of Key Points

---

1. The dc component of a converter waveform is given by its average value, or the integral over one switching period, divided by the switching period. Solution of a dc-dc converter to find its dc, or steady-state, voltages and currents therefore involves averaging the waveforms.

2. The linear ripple approximation greatly simplifies the analysis. In a well-designed converter, the switching ripples in the inductor currents and capacitor voltages are small compared to the respective dc components, and can be neglected.

3. The principle of inductor volt-second balance allows determination of the dc voltage components in any switching converter. In steady-state, the average voltage applied to an inductor must be zero.

# Summary of Chapter 2

---

4. The principle of capacitor charge balance allows determination of the dc components of the inductor currents in a switching converter. In steady-state, the average current applied to a capacitor must be zero.

5. By knowledge of the slopes of the inductor current and capacitor voltage waveforms, the ac switching ripple magnitudes may be computed. Inductance and capacitance values can then be chosen to obtain desired ripple magnitudes.

6. In converters containing multiple-pole filters, continuous (nonpulsating) voltages and currents are applied to one or more of the inductors or capacitors. Computation of the ac switching ripple in these elements can be done using capacitor charge and/or inductor flux-linkage arguments, without use of the small-ripple approximation.

7. Converters capable of increasing (boost), decreasing (buck), and inverting the voltage polarity (buck-boost and Cuk) have been described. Converter circuits are explored more fully in a later chapter.

# Chapter 3: Steady-State Equivalent Circuit Modeling, Losses, and Efficiency

- ▶ 3.1 The dc transformer model

- ▶ 3.2 Inclusion of inductor copper loss

- ▶ 3.3 Construction of equivalent circuit model

- ▶ 3.4 How to obtain the input port of the model

- ▶ 3.5 Example: inclusion of semiconductor conduction losses in the boost converter model

- ▶ 3.6 Summary of key points

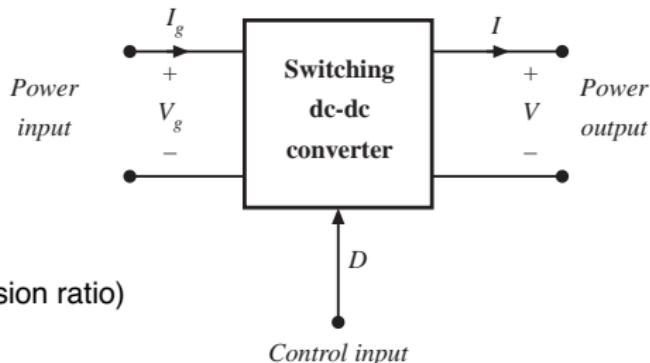

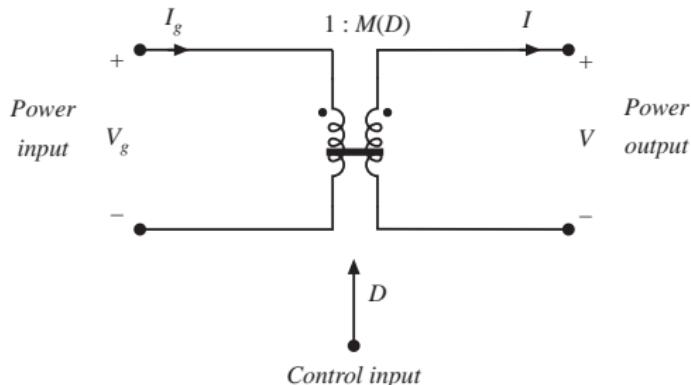

### 3.1. The dc transformer model

Basic equations of an ideal dc-dc converter:

$$P_{in} = P_{out} \quad (\eta = 100\%)$$

$$V_g I_g = V I$$

$$V = M(D) V_g \quad (\text{ideal conversion ratio})$$

$$I_g = M(D) I$$

These equations are valid in steady-state. During transients, energy storage within filter elements may cause  $P_{in} \neq P_{out}$

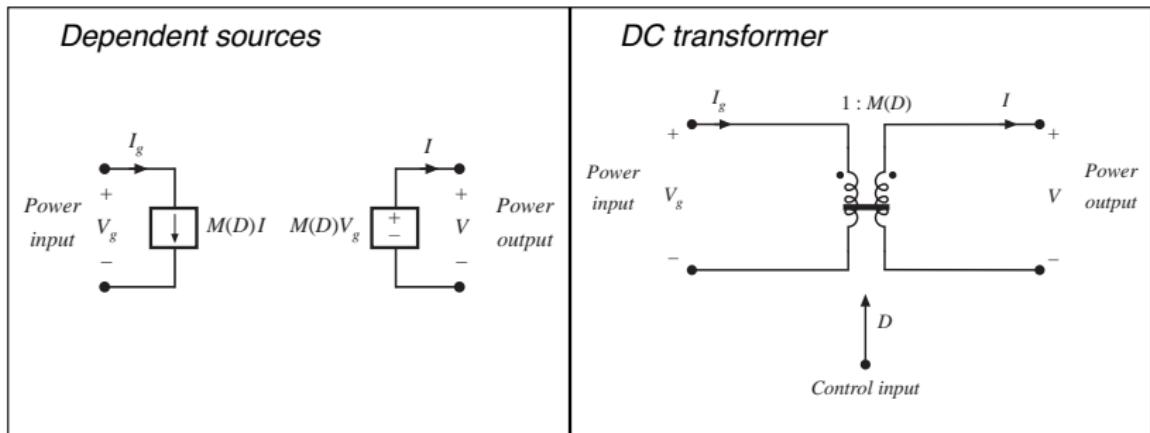

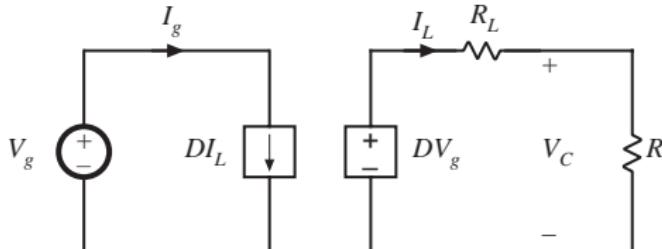

# Equivalent circuits corresponding to ideal dc-dc converter equations

$$P_{in} = P_{out} \quad V_g I_g = V I \quad V = M(D) V_g \quad I_g = M(D) I$$

# The DC transformer model

Models basic properties of ideal dc-dc converter:

- conversion of dc voltages and currents, ideally with 100% efficiency

- conversion ratio  $M$  controllable via duty cycle

- Solid line denotes ideal transformer model, capable of passing dc voltages and currents

- Time-invariant model (no switching) which can be solved to find dc components of converter waveforms

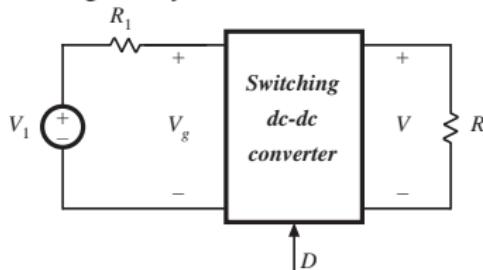

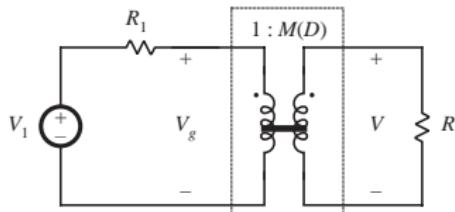

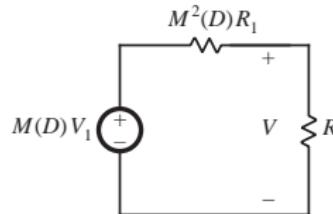

## Example: use of the DC transformer model

### 1. Original system

### 2. Insert dc transformer model

### 3. Push source through transformer

### 4. Solve circuit

$$V = M(D) V_1 \frac{R}{R + M^2(D) R_1}$$

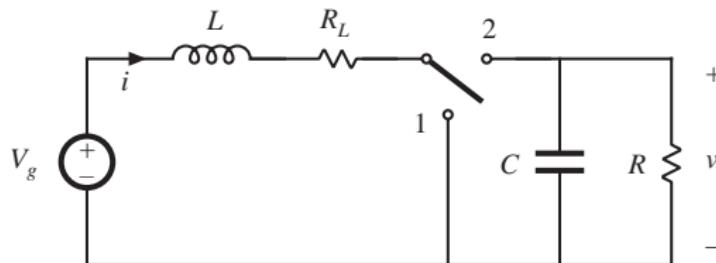

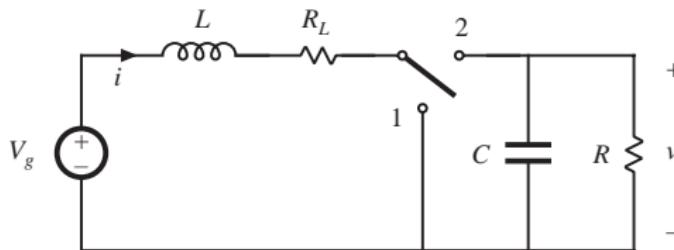

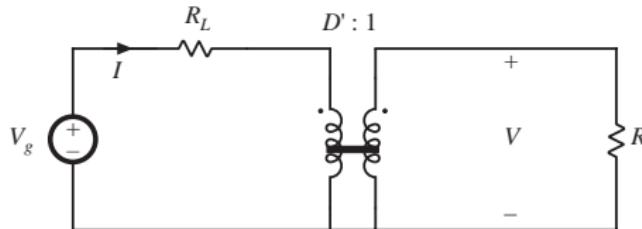

## 3.2. Inclusion of inductor copper loss

Dc transformer model can be extended, to include converter nonidealities.

Example: inductor copper loss (resistance of winding):

Insert this inductor model into boost converter circuit:

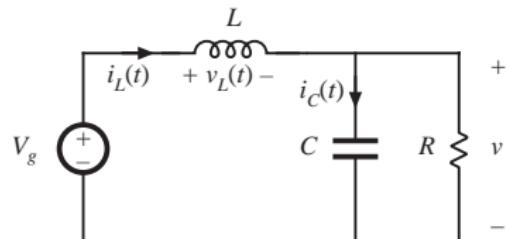

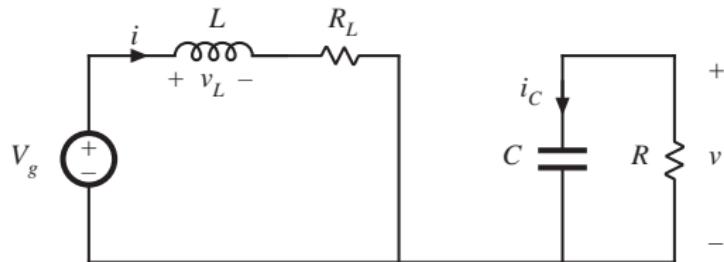

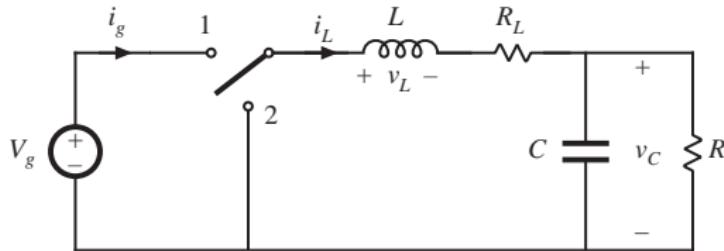

# Analysis of nonideal boost converter

switch in position 1

switch in position 2

# Circuit equations, switch in position 1

Inductor current and capacitor voltage:

$$v_L(t) = V_g - i(t) R_L$$

$$i_c(t) = -v(t) / R$$

Small ripple approximation:

$$v_L(t) = V_g - I R_L$$

$$i_c(t) = -V / R$$

## Circuit equations, switch in position 2

$$v_L(t) = V_g - i(t) R_L - v(t) \approx V_g - I R_L - V$$

$$i_C(t) = i(t) - v(t) / R \approx I - V / R$$

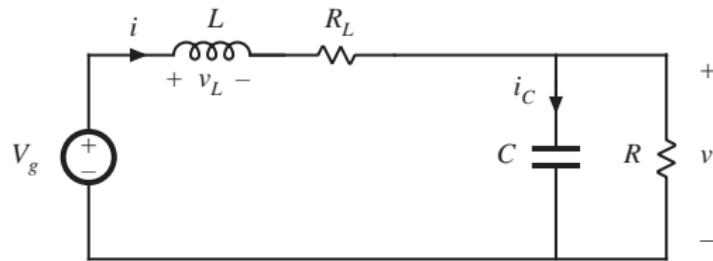

# Inductor voltage and capacitor current waveforms

Average inductor voltage:

$$\begin{aligned}\langle v_L(t) \rangle &= \frac{1}{T_s} \int_0^{T_s} v_L(t) dt \\ &= D(V_g - I R_L) + D'(V_g - I R_L - V)\end{aligned}$$

Inductor volt-second balance:

$$0 = V_g - I R_L - D'V$$

Average capacitor current:

$$\langle i_C(t) \rangle = D(-V/R) + D'(I - V/R)$$

Capacitor charge balance:

$$0 = D'I - V/R$$

$v_L(t)$

$i_C(t)$

# Solution for output voltage

We now have two equations and two unknowns:

$$0 = V_g - I R_L - D'V$$

$$0 = D'I - V / R$$

Eliminate  $I$  and solve for  $V$ :

$$\frac{V}{V_g} = \frac{1}{D'} \frac{1}{(1 + R_L / D'^2 R)}$$

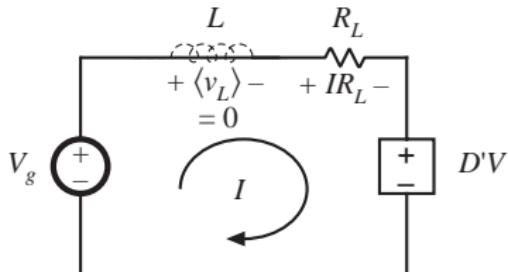

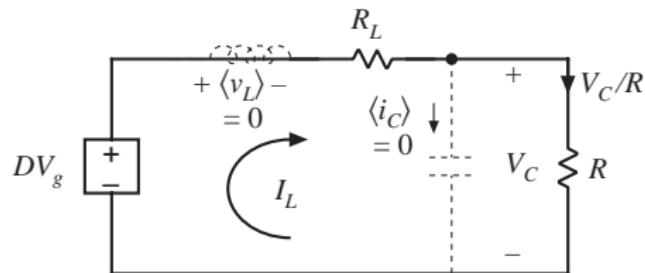

### 3.3. Construction of equivalent circuit model

---

Results of previous section (derived via inductor volt-sec balance and capacitor charge balance):

$$\langle v_L \rangle = 0 = V_g - I R_L - D'V$$

$$\langle i_c \rangle = 0 = D'I - V / R$$

View these as loop and node equations of the equivalent circuit.

Reconstruct an equivalent circuit satisfying these equations

# Inductor voltage equation

$$\langle v_L \rangle = 0 = V_g - IR_L - D'V$$

- Derived via Kirchhoff's voltage law, to find the inductor voltage during each subinterval

- Average inductor voltage then set to zero

- This is a loop equation: the dc components of voltage around a loop containing the inductor sum to zero

- $IR_L$  term: voltage across resistor of value  $R_L$  having current  $I$

- $D'V$  term: for now, leave as dependent source

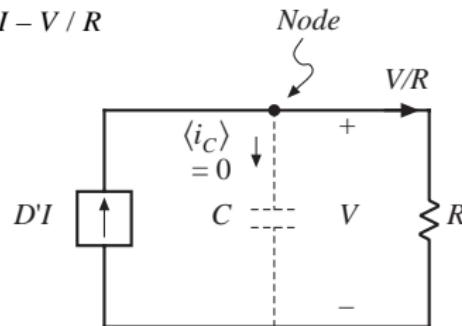

# Capacitor current equation

$$\langle i_c \rangle = 0 = D'I - V / R$$

- Derived via Kirchoff's current law, to find the capacitor current during each subinterval

- Average capacitor current then set to zero

- This is a node equation: the dc components of current flowing into a node connected to the capacitor sum to zero

- $V/R$  term: current through load resistor of value  $R$  having voltage  $V$

- $D'I$  term: for now, leave as dependent source

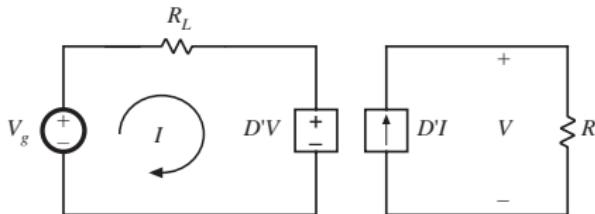

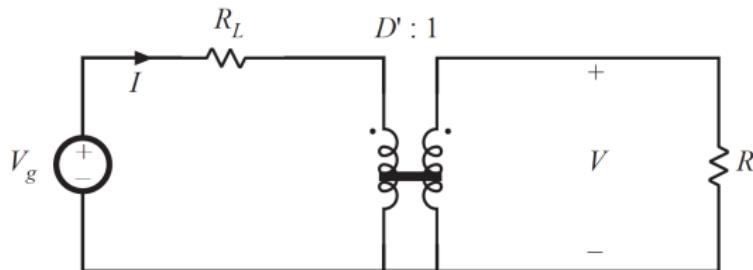

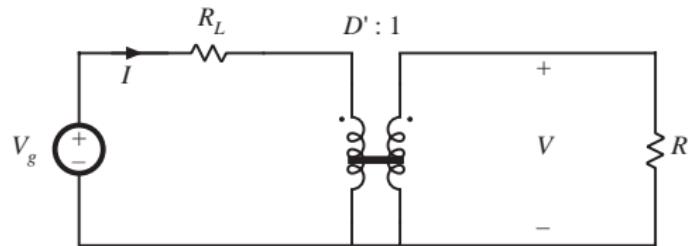

# Complete equivalent circuit

The two circuits, drawn together:

The dependent sources are equivalent to a  $D':1$  transformer:

Dependent sources and transformers

- sources have same coefficient

- reciprocal voltage/current dependence

# Solution of equivalent circuit

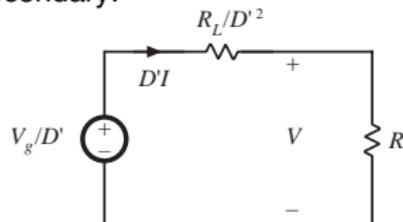

## Converter equivalent circuit

Refer all elements to transformer secondary:

Solution for output voltage using voltage divider formula:

$$V = \frac{V_g}{D'} \frac{R}{R + \frac{R_L}{D'^2}} = \frac{V_g}{D'} \frac{1}{1 + \frac{R_L}{D'^2 R}}$$

# Solution for input (inductor) current

$$I = \frac{V_g}{D'^2 R + R_L} = \frac{V_g}{D'^2 R} \frac{1}{1 + \frac{R_L}{D'^2 R}}$$

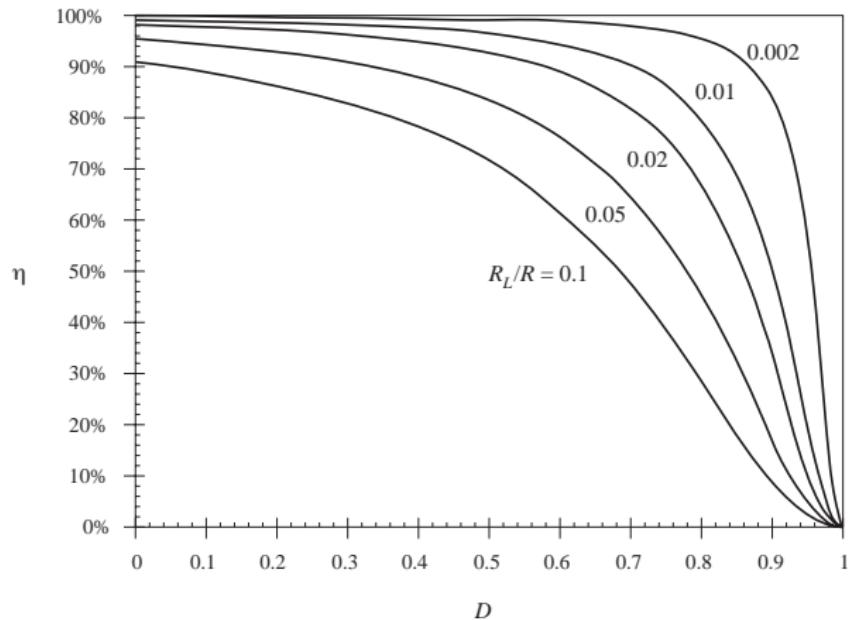

# Solution for converter efficiency

$$P_{in} = (V_g) (I)$$

$$P_{out} = (V) (D'I)$$

$$\eta = \frac{P_{out}}{P_{in}} = \frac{(V) (D'I)}{(V_g) (I)} = \frac{V}{V_g} D'$$

$$\eta = \frac{1}{1 + \frac{R_L}{D'^2 R}}$$

# Efficiency, for various values of $R_L$

$$\eta = \frac{1}{1 + \frac{R_L}{D^2 R}}$$

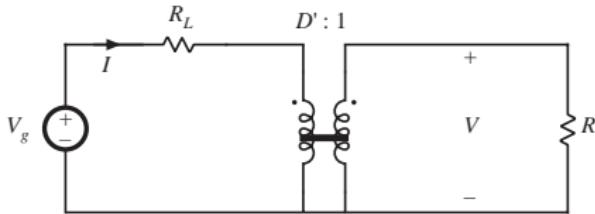

### 3.4. How to obtain the input port of the model

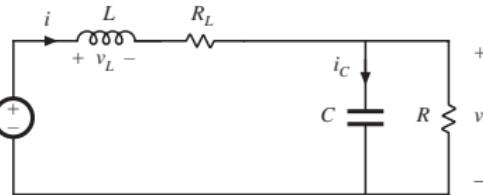

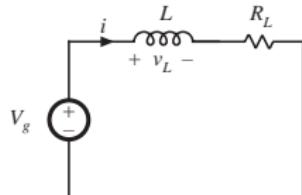

Buck converter example —use procedure of previous section to derive equivalent circuit

Average inductor voltage and capacitor current:

$$\langle v_L \rangle = 0 = DV_g - I_L R_L - V_C$$

$$\langle i_C \rangle = 0 = I_L - V_C / R$$

Construct equivalent circuit as usual

$$\langle v_L \rangle = 0 = DV_g - I_L R_L - V_C \quad \langle i_C \rangle = 0 = I_L - V_C / R$$

What happened to the transformer?

- Need another equation

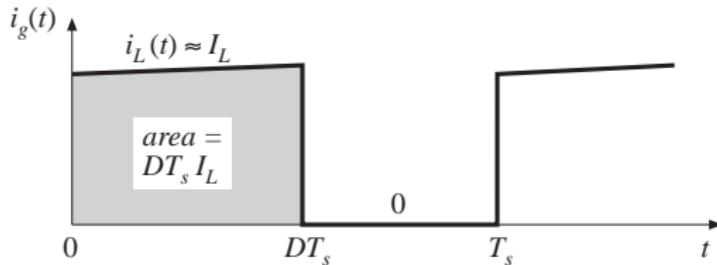

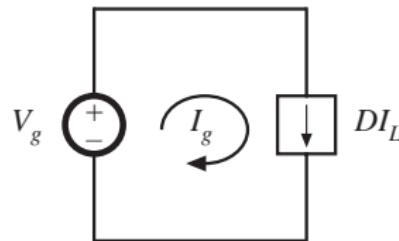

# Modeling the converter input port

Input current waveform  $i_g(t)$ :

Dc component (average value) of  $i_g(t)$  is

$$I_g = \frac{1}{T_s} \int_0^{T_s} i_g(t) dt = DI_L$$

# Input port equivalent circuit

---

$$I_g = \frac{1}{T_s} \int_0^{T_s} i_g(t) dt = DI_L$$

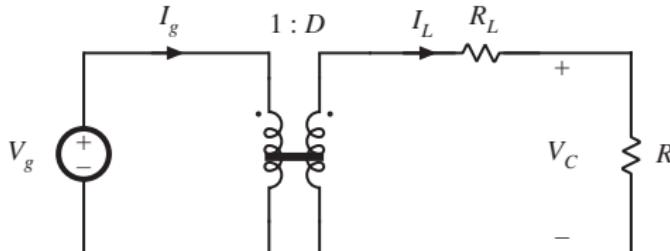

# Complete equivalent circuit, buck converter

Input and output port equivalent circuits, drawn together:

Replace dependent sources with equivalent dc transformer:

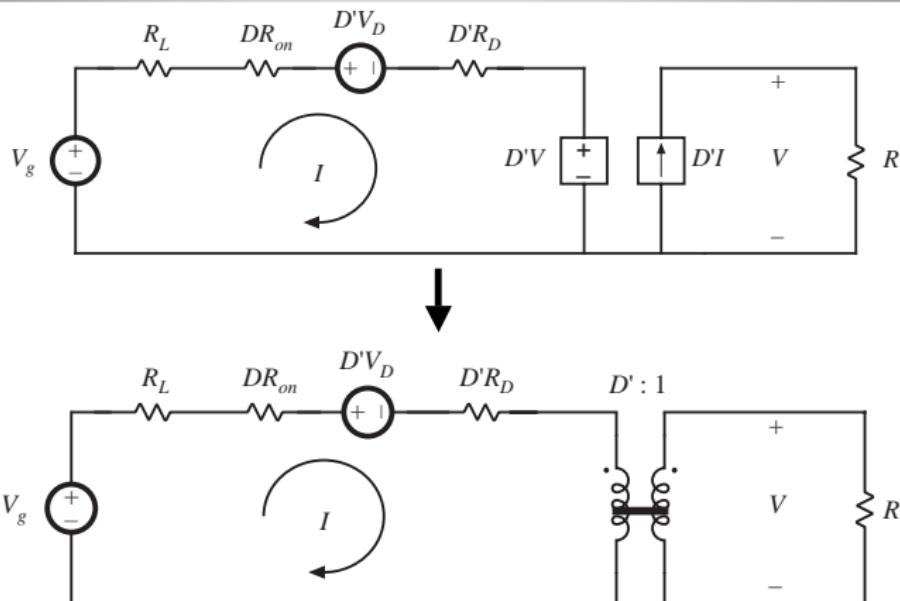

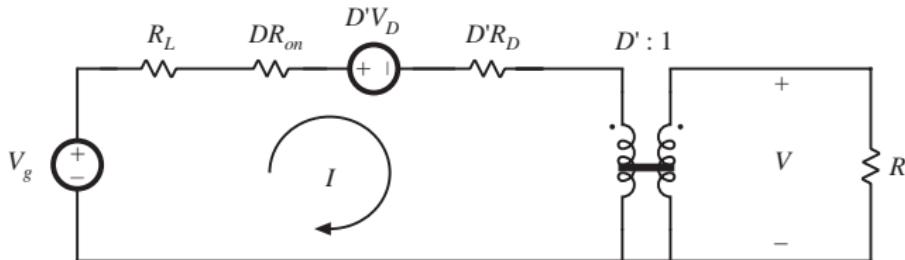

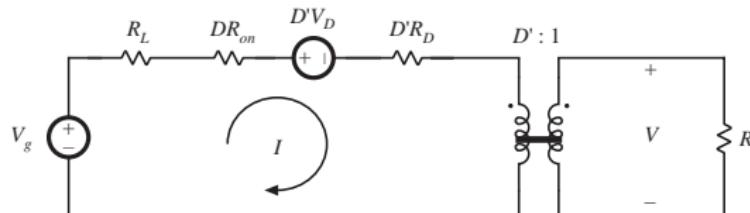

### 3.5. Example: inclusion of semiconductor conduction losses in the boost converter model

#### Boost converter example

Models of on-state semiconductor devices:

MOSFET: on-resistance  $R_{on}$

Diode: constant forward voltage  $V_D$  plus on-resistance  $R_D$

Insert these models into subinterval circuits

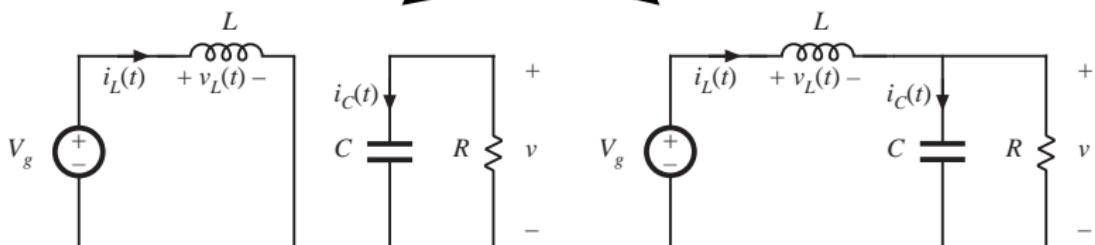

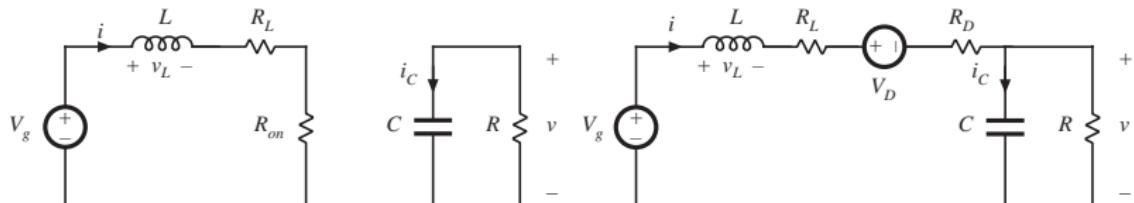

## Boost converter example: circuits during subintervals 1 and 2

*switch in position 1*

*switch in position 2*

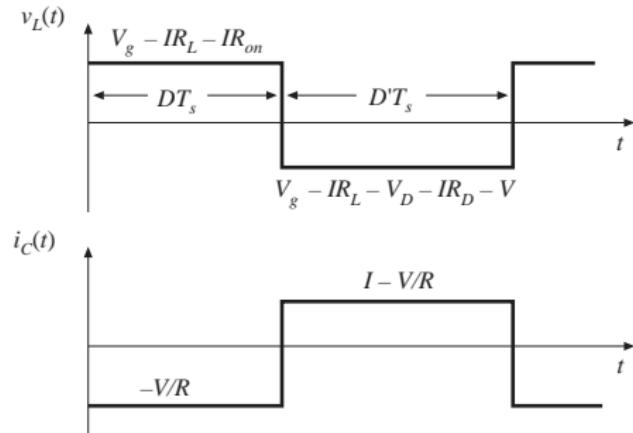

# Average inductor voltage and capacitor current

$$\langle v_L \rangle = D(V_g - IR_L - IR_{on}) + D'(V_g - IR_L - V_D - IR_D - V) = 0$$

$$\langle i_C \rangle = D(-V/R) + D'(I - V/R) = 0$$

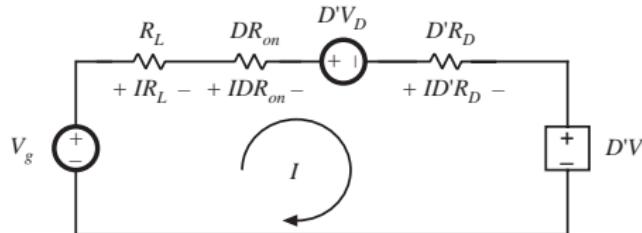

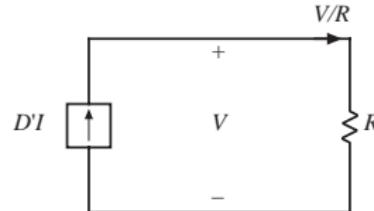

## Construction of equivalent circuits

$$V_g - IR_L - IDR_{on} - D'V_D - ID'R_D - D'V = 0$$

$$D'I - V/R = 0$$

# Complete equivalent circuit

## Solution for output voltage

$$V = \left( \frac{1}{D'} \right) \left( V_g - D'V_D \right) \left( \frac{D'^2 R}{D'^2 R + R_L + DR_{on} + D'R_D} \right)$$

$$\frac{V}{V_g} = \left( \frac{1}{D'} \right) \left( 1 - \frac{D'V_D}{V_g} \right) \left( \frac{1}{1 + \frac{R_L + DR_{on} + D'R_D}{D'^2 R}} \right)$$

# Solution for converter efficiency

$$P_{in} = (V_g) (I)$$

$$P_{out} = (V) (D'I)$$

$$\eta = D' \frac{V}{V_g} = \frac{\left(1 - \frac{D'V_D}{V_g}\right)}{\left(1 + \frac{R_L + DR_{on} + D'R_D}{D'^2 R}\right)}$$

*Conditions for high efficiency:*

$$V_g/D' \gg V_D$$

$$D'^2 R \gg R_L + DR_{on} + D'R_D$$

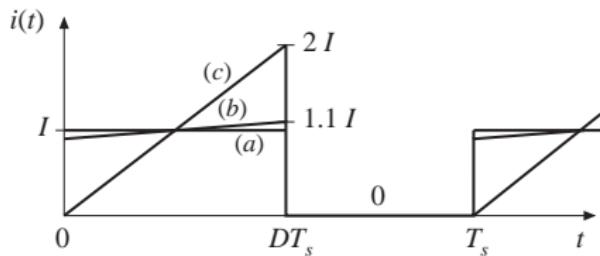

# Accuracy of the averaged equivalent circuit in prediction of losses

- Model uses average currents and voltages

- To correctly predict power loss in a resistor, use rms values

- Result is the same, provided ripple is small

*MOSFET current waveforms, for various ripple magnitudes:*

| Inductor current ripple | MOSFET rms current    | Average power loss in $R_{on}$ |

|-------------------------|-----------------------|--------------------------------|

| (a) $\Delta i = 0$      | $I \sqrt{D}$          | $D I^2 R_{on}$                 |

| (b) $\Delta i = 0.1 I$  | $(1.00167)I \sqrt{D}$ | $(1.0033) D I^2 R_{on}$        |

| (c) $\Delta i = I$      | $(1.155)I \sqrt{D}$   | $(1.3333) D I^2 R_{on}$        |

# Summary of chapter 3

---

1. The dc transformer model represents the primary functions of any dc-dc converter: transformation of dc voltage and current levels, ideally with 100% efficiency, and control of the conversion ratio  $M$  via the duty cycle  $D$ . This model can be easily manipulated and solved using familiar techniques of conventional circuit analysis.

2. The model can be refined to account for loss elements such as inductor winding resistance and semiconductor on-resistances and forward voltage drops. The refined model predicts the voltages, currents, and efficiency of practical nonideal converters.

3. In general, the dc equivalent circuit for a converter can be derived from the inductor volt-second balance and capacitor charge balance equations. Equivalent circuits are constructed whose loop and node equations coincide with the volt-second and charge balance equations. In converters having a pulsating input current, an additional equation is needed to model the converter input port; this equation may be obtained by averaging the converter input current.

# Chapter 4: Switch Realization

- ▶ Diode

- ▶ Structure

- ▶ Operation

- ▶ MOSFET

- ▶ Structure

- ▶ Operation

- ▶ IGBT

- ▶ Structure

- ▶ Operation

- ▶ Thyristor

- ▶ Structure

- ▶ Operation

- ▶ Wide-bandgap semiconductors

- ▶ Silicon Carbide

- ▶ Gallium Nitride

- ▶ MOSFET drivers

- ▶ Switch selection: controlled switch or diode?

- ▶ Other power semiconductors

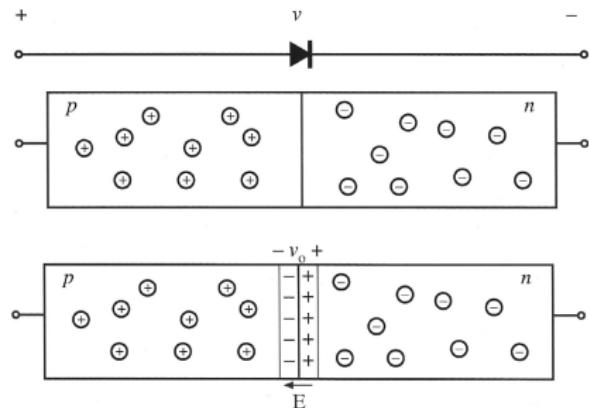

# Diode structure and principle

A p-n diode consists of two junctions:

- ▶ The n junction is doped with donor atoms, which contributes to the presence of electrons weakly bound to the lattice. These electrons can easily move (negative charges).

- ▶ The p junction is doped with acceptor atoms, which creates holes. These holes can move, creating a displacement of positive charges.

Figures from [4]:

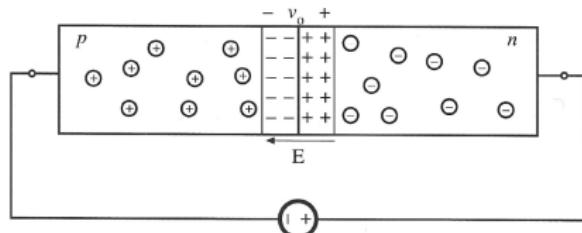

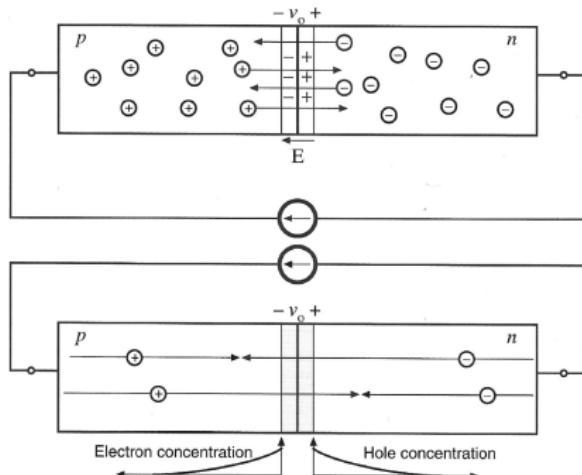

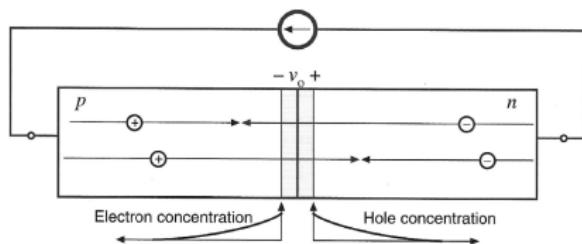

# Diode structure and principle

In reverse polarisation, minority carriers diffuse through the junction. A **depletion** region appears and creates an electric field that opposes the external voltage.

In forward polarisation, minority carriers diffuse through the junction and flow as minority carriers on the other side called **diffusion** region (electrons/holes diffuse through the junction to the p/n region respectively).

Figures from [4]

# Forward bias: charge-controlled behaviour

Minority charge concentration at the edge of the depletion region is related to the voltage across this region:

$$p_s(t) = Q_{s0}(e^{\lambda v(t)} - 1), \lambda = kT/q_e = 1/26 \text{ mV at } 300 \text{ K}$$

The total minority charge on one side follows:

$$\frac{dq(t)}{dt} = i(t) - \frac{q(t)}{\tau_L}$$

Figures from [4]

$\tau_L$  is the lifetime of the minority carrier.  $q(t)$  is proportional to  $p_s(t)$ , in steady-state ( $\frac{dq(t)}{dt} = 0$ ), we have:

$$i(t) = \frac{Q_0}{\tau_L}(e^{\lambda v(t)} - 1) = I_0(e^{\lambda v(t)} - 1)$$

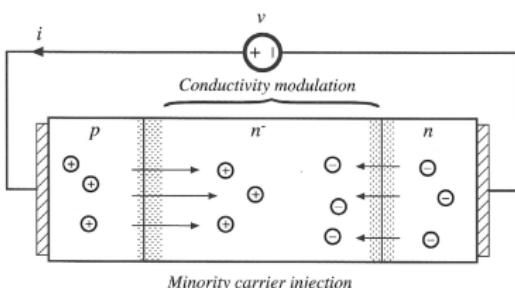

# Power diode structure

To support higher voltages, an intermediate lightly doped region (n-) is inserted :

- ▶ In reverse polarisation: a depletion region appears. For a given reverse voltage applied to the diode, the depletion region is wider and the electric field strength is weaker (compared to a diode constructed with a heavily doped region).

- ▶ In forward bias, due to the low doping, the n-zone has a higher resistance. By injecting carriers into this zone, the conductivity is modulated and this resistance is reduced.

Figures from [4]

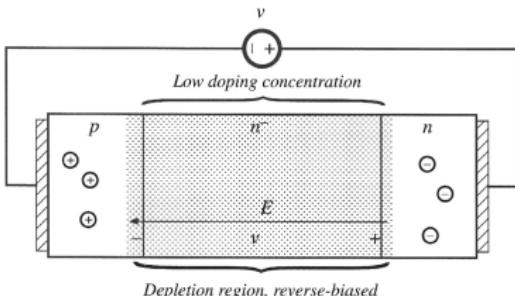

# Diode: static characteristic example

Excerpt of IXYS DSEP29-12A

data-sheet:

Fig. 1 Forward current  $I_F$  vs.  $V_F$

Current sharing in parallel diodes is difficult to achieve.

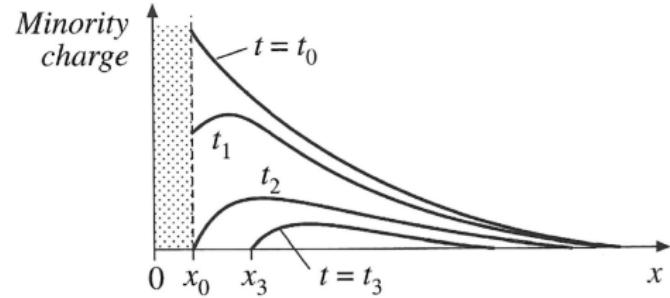

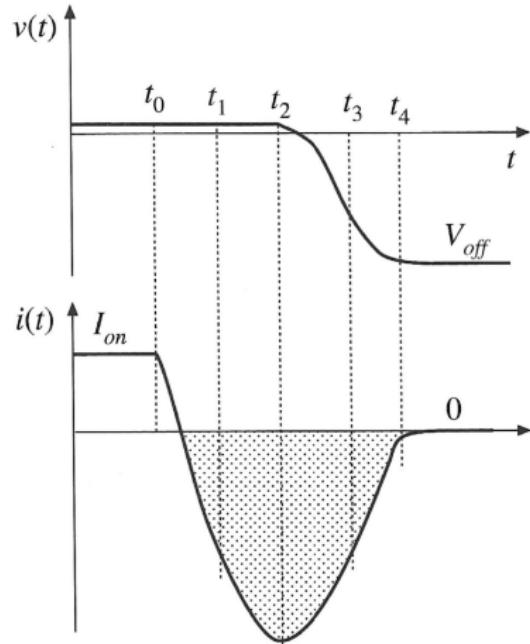

# Dynamic behaviour: reverse recovery transient

Figures from [4]

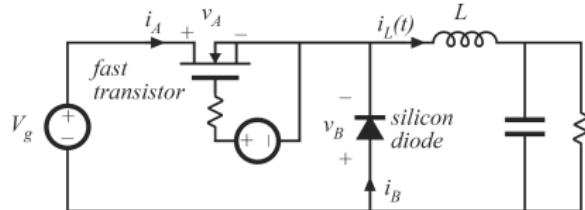

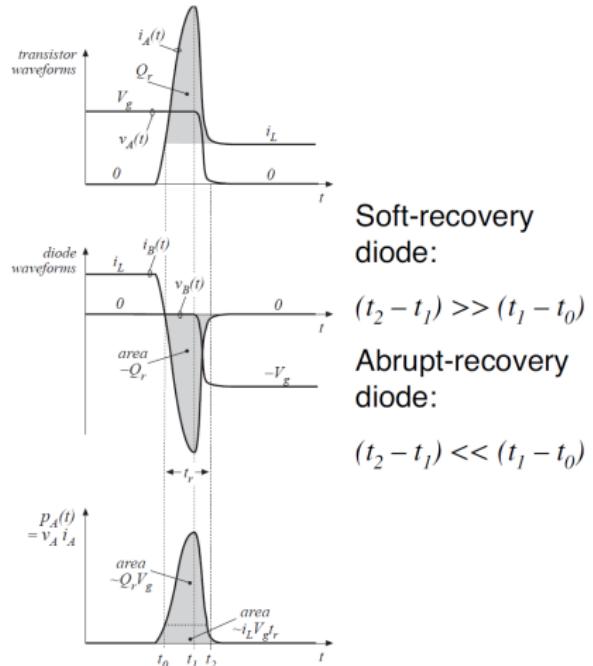

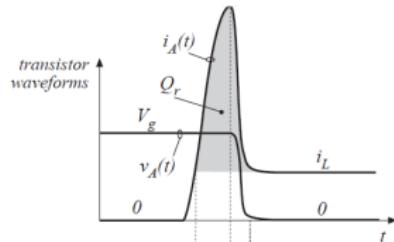

# Diode reverse recovery: transistor induced losses

- ▶ Diode recovered stored charge  $Q_r$  flows through transistor during transistor turn-on transition, inducing switching loss.

- ▶  $Q_r$  depends on diode current when turn-off starts and on the rate-of-change of diode current during diode turn-off transition.

Figures from [4]

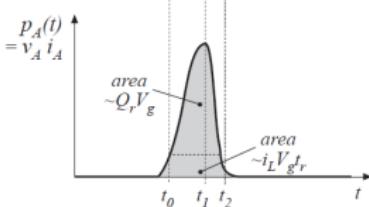

# Diode reverse recovery: transistor induced losses

Losses are induced in the transistor because the diode reverse voltage takes time to establish.

Assuming abrupt recovery, losses are essentially present in the transistor:

$$\begin{aligned} W_T &= \int_{t_0 \rightarrow t_1} v_A(t) i_A(t) dt \\ &\approx \int_{t_0 \rightarrow t_1} V_g (i_L - i_B(t)) dt \\ &= V_g i_L (t_1 - t_0) + V_g Q_r. \end{aligned}$$

Soft-recovery diode:

$$(t_2 - t_1) \gg (t_1 - t_0)$$

Abrupt-recovery diode:

$$(t_2 - t_1) \ll (t_1 - t_0)$$

Figures from [4]

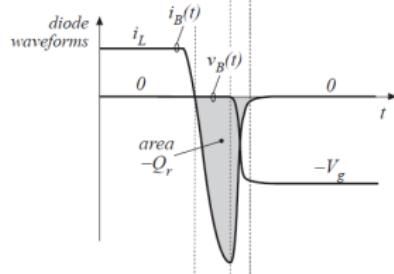

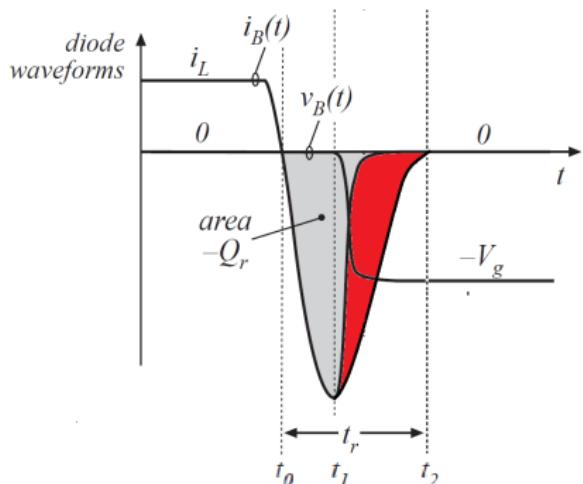

# Diode reverse recovery: diode losses

Once the transistor is closed, the diode sees the full voltage and experiences a non negligible trailing current (soft recovery case):

$$\begin{aligned} W_D &= \int_{t_1 \rightarrow t_2} v_B(t) i_B(t) dt \\ &\approx \int_{t_1 \rightarrow t_2} -V_g \cdot i_B(t) dt \\ &= -V_g \int_{t_1 \rightarrow t_2} i_B(t) dt \\ &= V_g Q_{red}. \end{aligned}$$

Modified figure of [1]

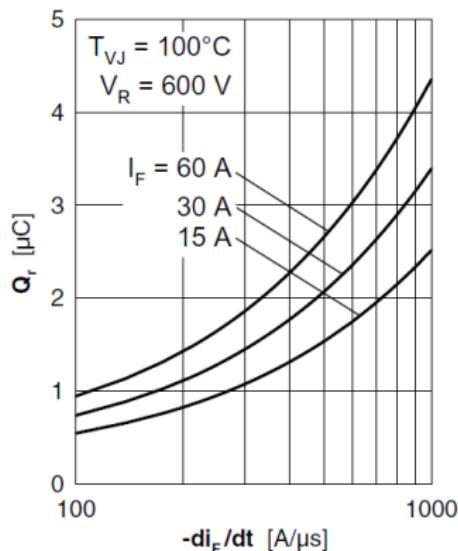

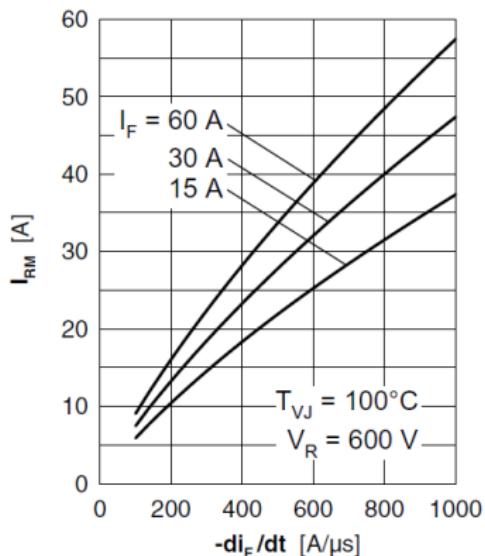

# Diode: recovery characteristics example

Excerpt of IXYS DSEP29-12A data-sheet:

Fig. 2 Typ. reverse recovery charge  $Q_r$  versus  $-\frac{di_F}{dt}$

Fig. 3 Typ. peak reverse current  $I_{RM}$  versus  $-\frac{di_F}{dt}$

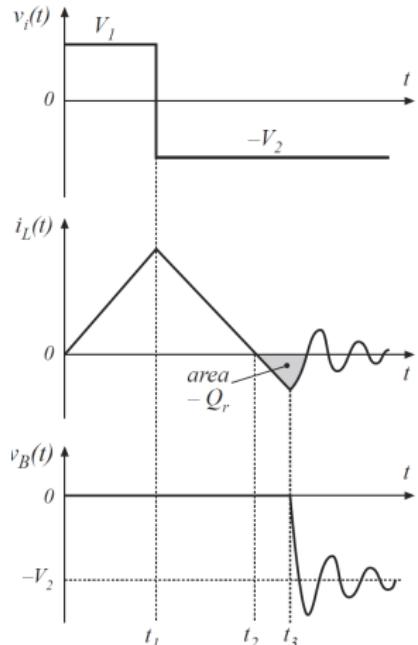

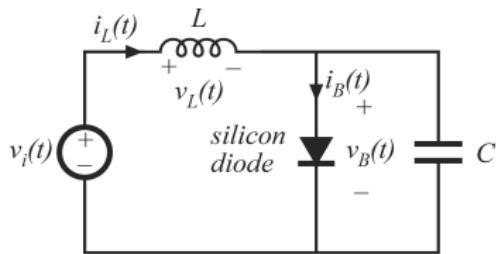

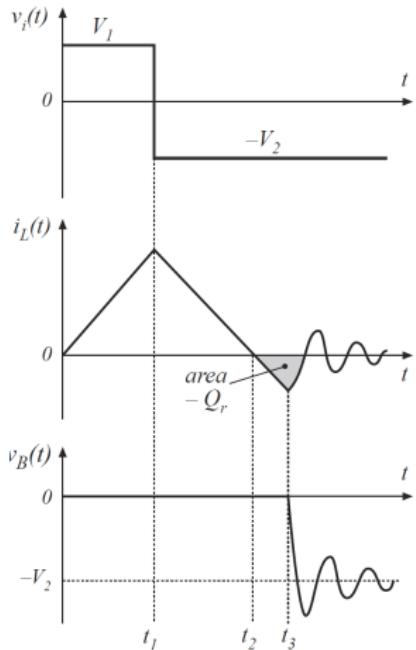

# Ringing induced by diode stored charge

- ▶  $t < t_2$ , diode forward-biased,  $i_L(t) > 0$ .

- ▶ Diode reverse recovery,  $i_L(t) < 0$ , stored charge  $Q_r$  are removed.

- ▶  $t > t_3$ , diode becomes reverse-biased, L-C network oscillates due to initial negative inductor current.

- ▶ Oscillation damped and ringing energy is lost.

Figures from [4]

# Energy associated with ringing

Recovered charge is  $Q_r = - \int_{t_2}^{t_3} i_L(t) dt$

Energy stored in inductor during interval:

$$t_2 \leq t \leq t_3: E_L = \int_{t_2}^{t_3} v_L(t) i_L(t) dt$$

Applied inductor voltage during interval:

$$t_2 \leq t \leq t_3: v_L(t) = L \frac{di_L(t)}{dt} = -V_2$$

Hence,

$$E_L = \int_{t_2}^{t_3} L \frac{di_L(t)}{dt} i_L(t) dt = \int_{t_2}^{t_3} (-V_2) i_L(t) dt$$

$$E_L = \frac{1}{2} L i_L^2(t_3) = V_2 Q_r$$

Figures from [4]

# Characteristics of several commercial diodes

| Part number                   | Rated maximum voltage | Rated average current | $V_F$ (typical) | $t_r$ (max) |

|-------------------------------|-----------------------|-----------------------|-----------------|-------------|

| Fast recovery rectifiers      |                       |                       |                 |             |

| IN3913                        | 400 V                 | 30 A                  | 1.1 V           | 400 ns      |

| SD453N2S20PC                  | 2500 V                | 400 A                 | 2.2 V           | 3 $\mu$ s   |

| Ultrafast recovery rectifiers |                       |                       |                 |             |

| MUR815                        | 150 V                 | 8 A                   | 0.975 V         | 35 ns       |

| RHRD660                       | 600 V                 | 6 A                   | 1.7 V           | 35 ns       |

| RHRU100120                    | 1200 V                | 100 A                 | 2.6 V           | 60 ns       |

| Schottky rectifiers           |                       |                       |                 |             |

| MBR6030L                      | 30 V                  | 60 A                  | 0.48 V          |             |

| 444CNQ045                     | 45 V                  | 440 A                 | 0.69 V          |             |

| 30CPQ150                      | 150 V                 | 30 A                  | 1.19 V          |             |

| SiC Schottky rectifiers       |                       |                       |                 |             |

| C4D10120E                     | 1200 V                | 10 A                  | 1.8 V           |             |

| C3D3060F                      | 600 V                 | 3 A                   | 1.7 V           |             |

Table from [4]

Diode are compromises between rated maximum voltage, rated average current, voltage drop ( $V_F$ ), reverse recovery time ( $t_r$ ). Schottky diode consists of a direct junction between a metal and an n-type semiconductor, forming a Schottky barrier rather than a traditional P-N junction.

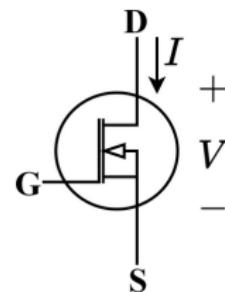

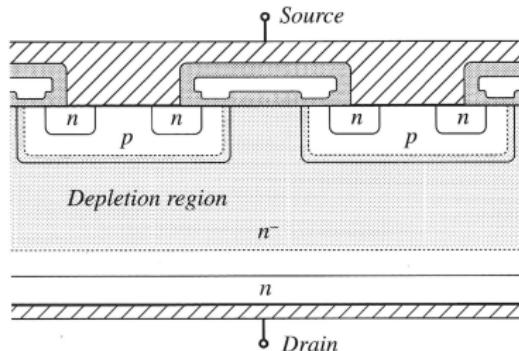

# MOSFET: structure

Figures from [4]

- ▶ A cross-section of a DMOS n-channel cell is shown ( $\approx 1 \mu m$ ).

- ▶ Crosshatched regions are metallized contacts.

- ▶ Shaded regions are insulating oxide layers.

- ▶ A power MOSFET consists of thousands of MOSFETs cells connected in parallel.

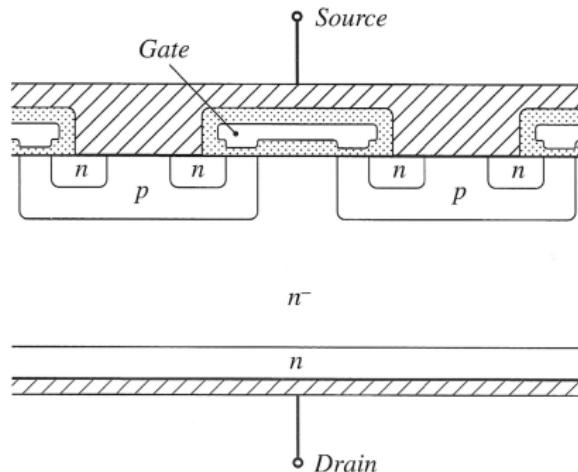

# MOSFET: ON/OFF state

OFF state: the gate is not biased and a positive drain-source voltage is applied. The MOSFET behaves like a reverse-biased diode and the depletion region appears within the n- region.

ON state: a positive voltage is applied between the gate and the source, creating an inversion region under the gate, which contains mobile electrons capable of conducting drain-source current (**drift** region).

Note: there is no conductivity modulation effect as in a diode.

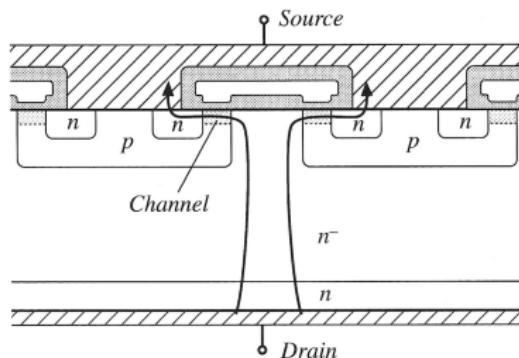

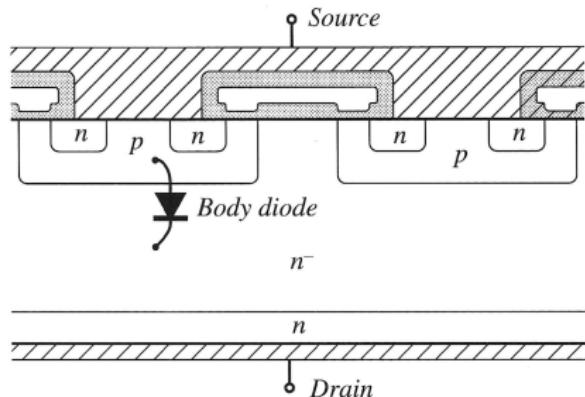

# MOSFET: body diode

The p-n- junction forms an effective diode, in parallel with the channel.

Figures from [4]

- ▶ A negative drain-to source voltage can forward-bias the body diode.

- ▶ The body diode can conduct the full MOSFET rated current.

- ▶ The body diode switching speed not optimized,  $Q_r$  is large.

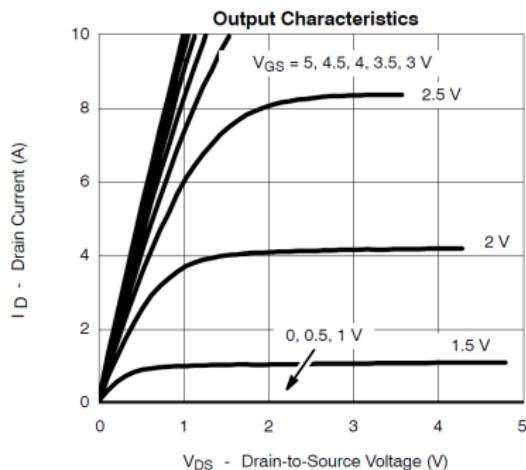

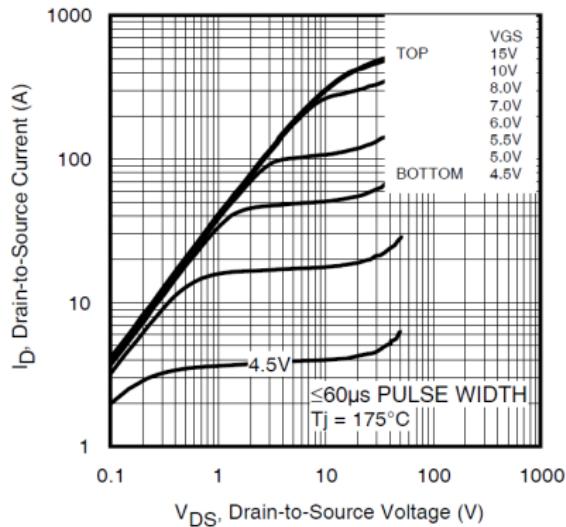

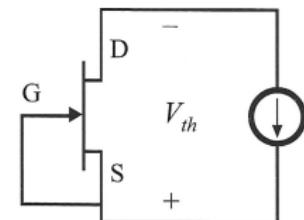

# Typical MOSFET static characteristics

Excerpt of Vishay Si2301DS MOSFET data-sheet:

Note: MOSFET can conduct peak current well in excess of average current rating.

- ▶  $V_{GS} < V_{th}$ : OFF state

- ▶  $V_{GS} \gg V_{th}$ : ON state

- ▶  $V_{DS} \ll$ : D-S channel modelled by  $R_{DSon}$ .

- ▶  $V_{DS} \gg$ : D-S channel modelled  $I = G(V_{GS} - V_{th})$ ,  $G$  is the transconductance.

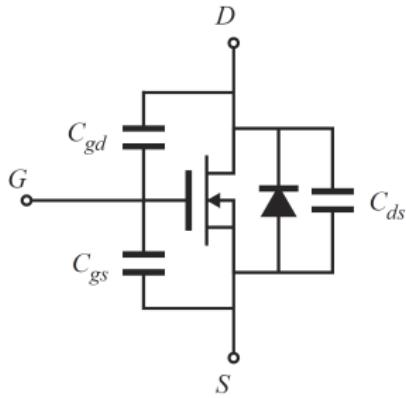

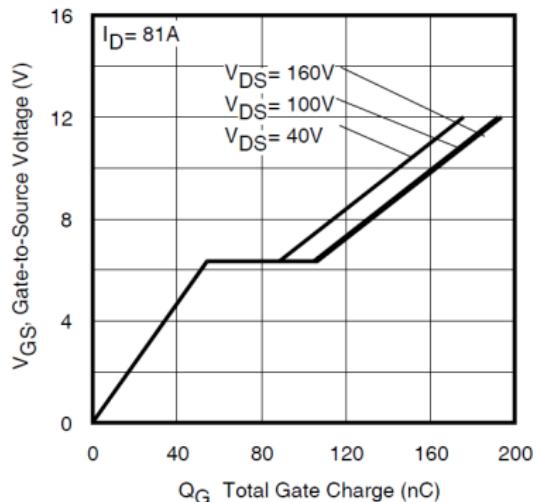

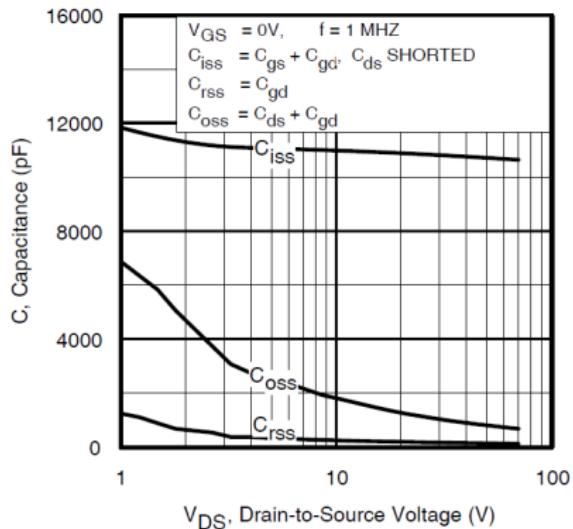

# MOSFET dynamic equivalent circuit

- ▶  $C_{gs}$ : large gate-source capacitance, essentially constant

- ▶  $C_{gd}$ : small gate-drain capacitance, highly nonlinear

- ▶  $C_{ds}$ : intermediate in value drain-source capacitance, highly nonlinear

- ▶ Switching time function of driver current that charges/discharges  $C_{gs}$  and  $C_{gd}$

Figures from [4]

$$C_{ds}(v_{ds}) = \frac{C_0}{\sqrt{1 + \frac{v_{ds}}{V_0}}}$$

$$C_{ds}(v_{ds}) \approx C_0 \sqrt{\frac{V_0}{v_{ds}}} = \frac{C'_0}{\sqrt{v_{ds}}}$$

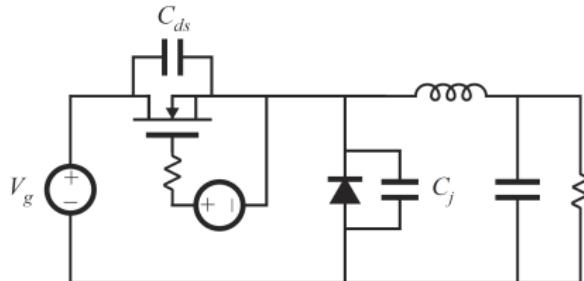

# Switching loss: parasitic capacitances

Example, the buck converter:

Figures from [4]

Energy lost during MOSFET turn-on transition (assuming linear capacitances) is the energy stored in the parasitic capacitances:

$$E_C = \frac{1}{2} (C_{ds} + C_j) V_g^2$$

## MOSFET nonlinear $C_{ds}$

Incremental  $C_{ds}(v_{ds})$  is approximated by:  $C_{ds}(v_{ds}) \approx \frac{C'_0}{\sqrt{v_{ds}}}$ .

The energy stored in  $C_{ds}$  at  $v_{ds} = V_{DS}$ :

$$\begin{aligned} E_{C_{ds}} &= \int v_{ds} i_C dt = \int v_{ds} C_{ds}(v_{ds}) \frac{dv_{ds}(t)}{dt} dt = \int_0^{V_{DS}} v_{ds} C_{ds}(v_{ds}) dv_{ds} \\ &= \int_0^{V_{DS}} \frac{C'_0}{\sqrt{v_{ds}}} v_{ds} dv_{ds} = \int_0^{V_{DS}} C'_0 \sqrt{v_{ds}} dv_{ds} \\ &= \frac{2}{3} C'_0 V_{DS}^{\frac{3}{2}} = \frac{2}{3} \frac{C'_0}{\sqrt{V_{DS}}} V_{DS}^2 = \frac{1}{2} \frac{4}{3} C_{ds}(V_{DS}) V_{DS}^2. \end{aligned}$$

The energy loss is equivalent to the energy loss related to a voltage independant capacitor but taking  $\frac{4}{3}$  of the capacitance value at  $V_{ds}$ .

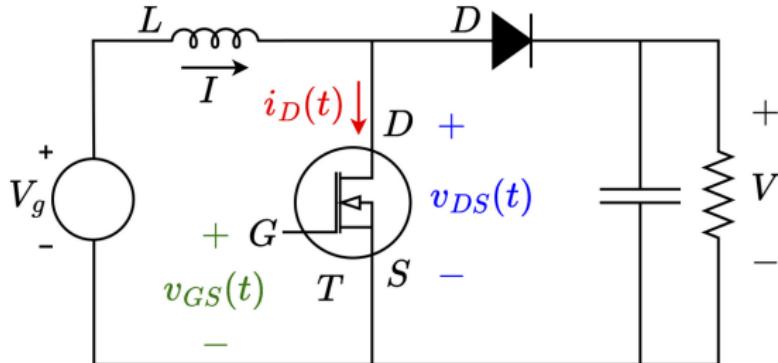

# MOSFET: hard switching loss circuit example

Figures from [4]

- ▶ Boost converter considered.

- ▶ The reasoning also applied to other circuits in hard switching.

- ▶ Diode D is considered ideal in this case.

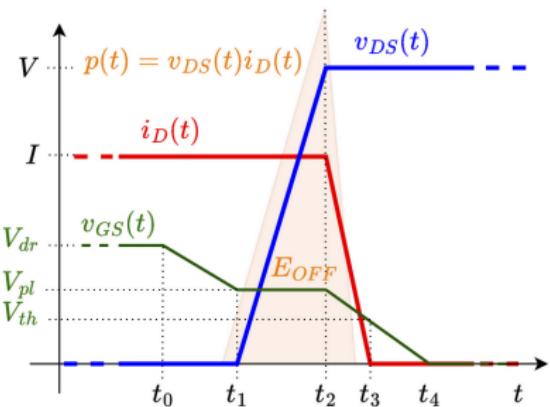

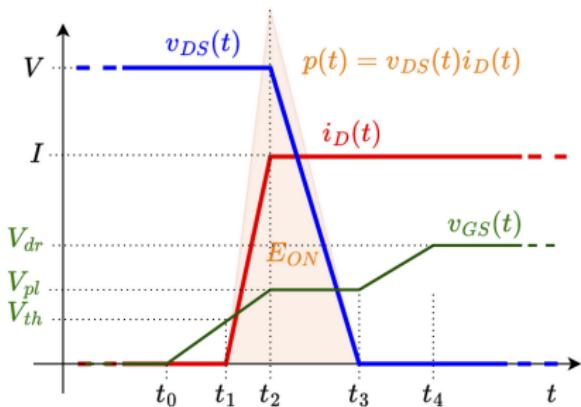

# MOSFET: hard switching losses waveforms

Power losses = area  $E_{on}$  and  $E_{off}$  (energy) times  $f_s$  (switching frequency):

$$P_{ON} = \frac{1}{2} V \cdot I \cdot (t_3 - t_1) \cdot f_s$$

$$P_{OFF} = \frac{1}{2} V \cdot I \cdot (t_3 - t_1) \cdot f_s$$

Rebuild the diagram.

# MOSFET: hard switching losses explanations

Turn-On (left figure on previous slide):

$t_0 \rightarrow t_1$ : the gate voltage  $v_{GS}(t)$  rises from 0 to  $V_{th}$ .

$t_1 \rightarrow t_2$ : the drain current  $i_{DS}(t)$  rises according to  $v_{GS}(t)$  change:

$i_D(t) = G(v_{GS}(t) - V_{th})$ , G is the transconductance. Once  $i_{DS}(t)$  reaches  $I$ , the transistor carries the full load current.

$t_2 \rightarrow t_3$ :  $v_{GS}(t)$  stays at the "plateau" voltage  $V_{pl}$  due to the Miller effect and the drain voltage  $v_{DS}(t)$  falls linearly.

$t_3 \rightarrow t_4$ : once  $v_{DS}(t)$  reaches 0V at  $t_3$ ,  $v_{GS}(t)$  continues to rise up to  $V_{dr}$ .

Turn-Off (right figure on previous slide):

$t_0 \rightarrow t_1$ :  $v_{GS}(t)$  falls from  $V_{dr}$  to  $V_{pl}$ .

$t_1 \rightarrow t_2$ : when  $v_{GS}(t)$  reaches  $V_{pl}$ ,  $v_{DS}(t)$  starts rising linearly.  $v_{GS}(t)$  stays at  $V_{pl}$  due to the Miller effect.

$t_2 \rightarrow t_3$ : once  $v_{DS}(t)$  reaches  $V$ ,  $v_{GS}(t)$  starts falling again and  $i_{DS}(t)$  also starts falling accordingly:  $i_D(t) = G(v_{GS}(t) - V_{th})$ , G is the transconductance.

$t_3 \rightarrow t_4$ : once  $v_{GS}(t)$  reaches  $V_{th}$ ,  $i_{DS}(t)$  reaches 0V and  $v_{GS}(t)$  goes to 0V.

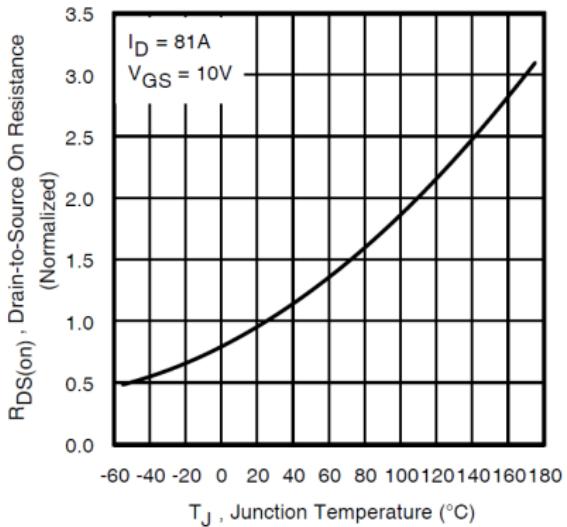

# MOSFET: static characteristics example

Excerpt of IR IRFP4668PbF MOSFET data-sheet:

$R_{DSon}$  has positive temperature coefficient, MOSFETs are therefore easy to parallel.

# MOSFET: dynamic characteristics example

Excerpt of IR IRFP4668PbF MOSFET data-sheet:

# Characteristics of several commercial power MOSFETs

| Part number | Rated maximum voltage | Rated average current | $R_{on}$ | $Q_g$ (typical) |

|-------------|-----------------------|-----------------------|----------|-----------------|

| SiSS64DN    | 30 V                  | 40 A                  | 2.1 mΩ   | 21 nC           |

| CSD18512Q5B | 40 V                  | 100 A                 | 1.3 mΩ   | 75 nC           |

| NTMFS6H800N | 80 V                  | 203 A                 | 1.8 mΩ   | 85 nC           |

| IXFH80N25X3 | 250 V                 | 80 A                  | 13 mΩ    | 83 nC           |

| IPL60R065P7 | 650 V                 | 41 A                  | 53 mΩ    | 67 nC           |

Table from [4]

- ▶ For a same rated maximum voltage, MOSFET with lower  $R_{on}$  have higher  $Q_g$ .

- ▶ For a same die size (same  $Q_g$ ), MOSFET with higher voltage have higher  $R_{on}$ .

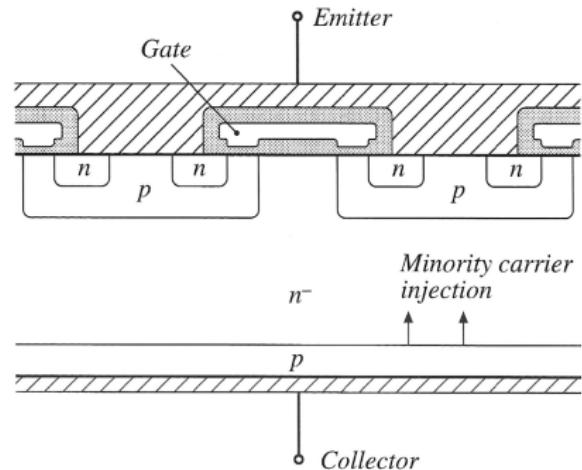

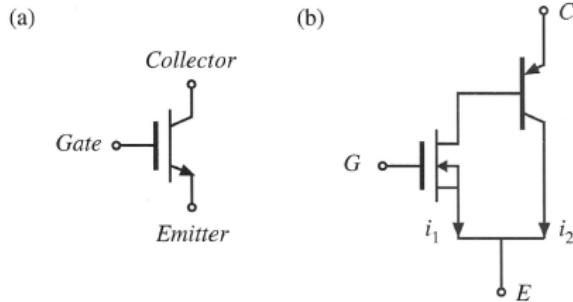

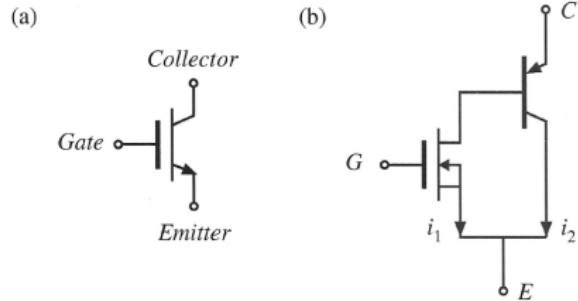

# IGBT: structure

- ▶ An IGBT (Insulated gate bipolar transistor) is bipolar transistor controlled by a MOSFET.

- ▶ Simple control like a MOSFET with current density of a bipolar transistor.

$$i_2 = \beta i_1,$$

$\beta$  is the bipolar transistor gain.

Figure from [4]

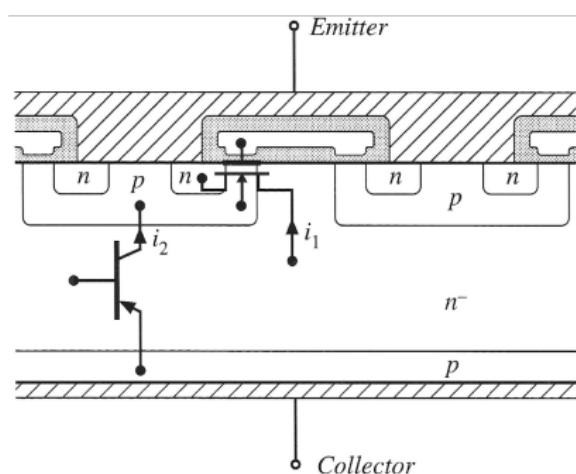

# IGBT: operation

- ▶ MOSFET controls the base current amplified by the bipolar transistor.

- ▶ Drawback: bipolar transistor is a minority carrier device

⇒ slower.

Figure from [4]

Show current to explain the way an IGBT operate.

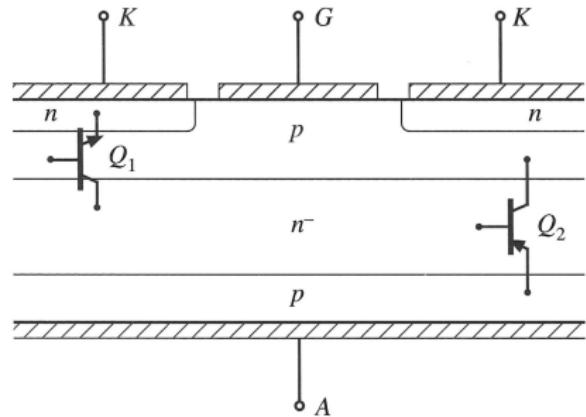

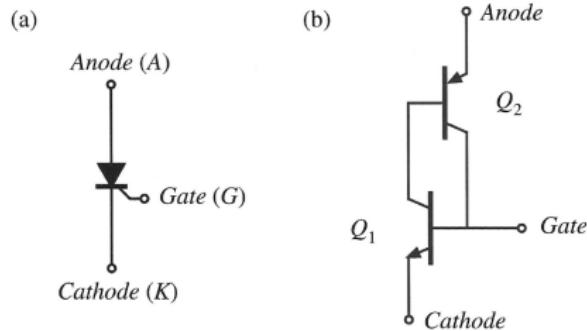

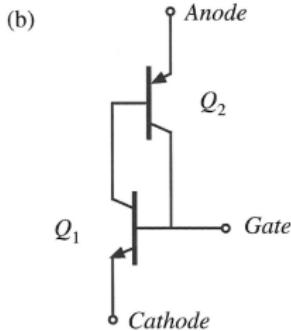

# Thyristor: structure

- ▶ A thyristor is an arrangement of two bipolar transistors.

- ▶ The two transistors control each other.

- ▶ One transistor can be controlled externally.

Figure from [4]

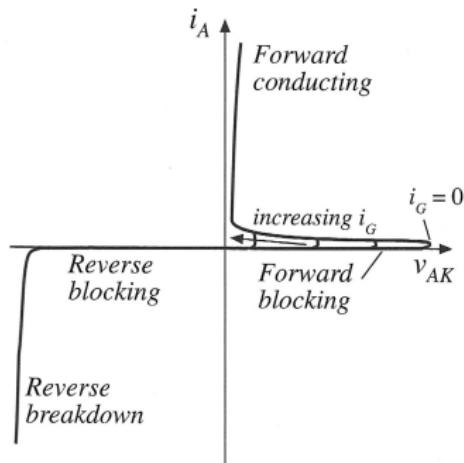

# Thyristor: operation

- ▶ Once started, the two transistors maintain each other's base currents.

- ▶ The current is only interrupted if the main current is lower than the holding current.

- ▶ Thyristors are slow but are robust and can drive very high current with high voltage.

Figure from [4]

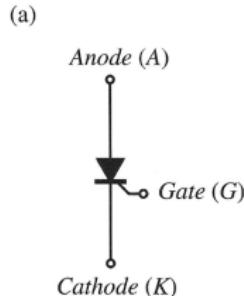

# Wide bandgap semiconductors

| Material | Bandgap [eV] | Electron mobility $\mu_n$ [cm <sup>2</sup> /Vs] | Permittivity $\epsilon_s$ | Critical field $E_c$ [V/cm] | Thermal conductivity [W/m <sup>0</sup> K] |

|----------|--------------|-------------------------------------------------|---------------------------|-----------------------------|-------------------------------------------|

| Si       | 1.1          | 1350                                            | 11.8                      | $3 \cdot 10^5$              | 150                                       |

| SiC (4H) | 3.26         | 720                                             | 10                        | $2 \cdot 10^6$              | 450                                       |

| GaN      | 3.44         | 1500–2000 (2DEG)                                | 9                         | $3.3 \cdot 10^6$            | 130                                       |

Table from [4]

$$A R_{on} = \frac{k}{\mu_n \epsilon_s E_c^3} V_B^2$$

Figure from [5]

$A$  : device area

$R_{on}$  : resistance of the drift region

$k$  : constant, function of the process

$V_B$  : breakdown voltage of the device

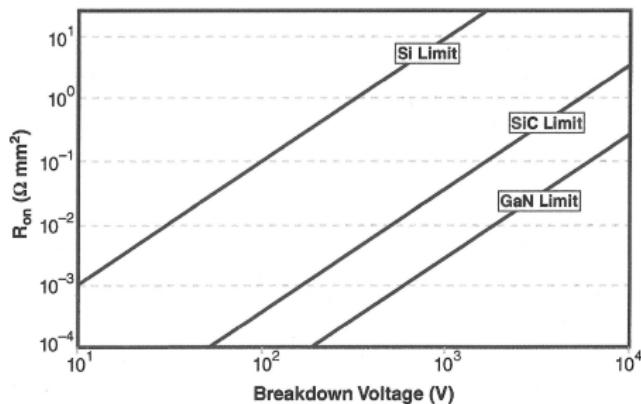

# Silicon Carbide (SiC) MOSFET

Figure from Microchip web site

- ▶ Si is replaced by SiC.

- ▶ The n- drift region of SiC is smaller than in Si devices due to the high critical field.

- ▶ SiC MOSFET are high voltage devices faster and with lower resistance than Si MOSFET.

| Part number     | Rated maximum voltage | Rated average current | $R_{on}$ | $Q_g$ (typical) |

|-----------------|-----------------------|-----------------------|----------|-----------------|

| C3M0030090K     | 900 V                 | 63 A                  | 30 mΩ    | 87 nC           |

| C3M0075120K     | 1200 V                | 30 A                  | 75 mΩ    | 51 nC           |

| C2M0045170D     | 1700 V                | 72 A                  | 45 mΩ    | 188 nC          |

| SCT3022AL       | 650 V                 | 93 A                  | 22 mΩ    | 133 nC          |

| CPM3-0900-0010A | 900 V                 | 196 A                 | 10 mΩ    | 68 nC           |

Table from [4]

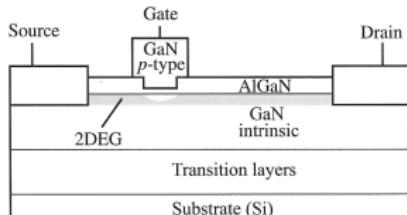

# Gallium Nitride FET

Figure from [4]

- ▶ GaN transistors are JFET.

- ▶ Current conduction is provided by a two-dimensional electron gas (2DEG).

- ▶ GaN has no reverse recovery.

- ▶ GaN are at least 10 times faster than Si MOSFET.

|                           | Si SJ MOSFET  | GaN FET     |

|---------------------------|---------------|-------------|

| Voltage rating            | 650 V         | 650 V       |

| $R_{on}$ , 25–150°C       | 24–60 mΩ      | 25–50 mΩ    |

| $Q_g$ at $V_{DS} = 400$ V | 123 nC (10 V) | 12 nC (6 V) |

| $V_{SD}$                  | 0.8 V         | 4 V         |

| $Q_{rr}$                  | 8.7 $\mu$ C   | –           |

| $t_{rr}$                  | 440 ns        | –           |

Table from [4]

Figure from [4]

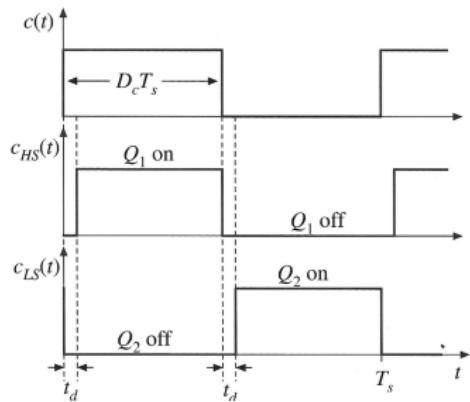

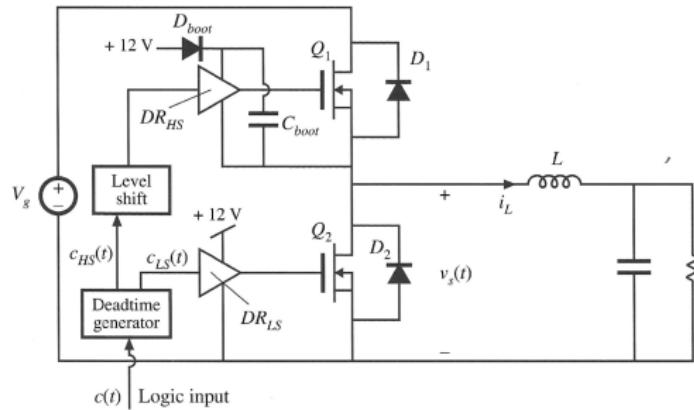

# MOSFET drivers structure

Figure from [4]

- ▶ Drivers have many functions: **voltage levels** adaptation, generate charge/discharge **current**, **deadtime** generation, **levelshift**.

- ▶ High side driver has to be supplied with floating supply: **isolated supply** or **bootstrap**.

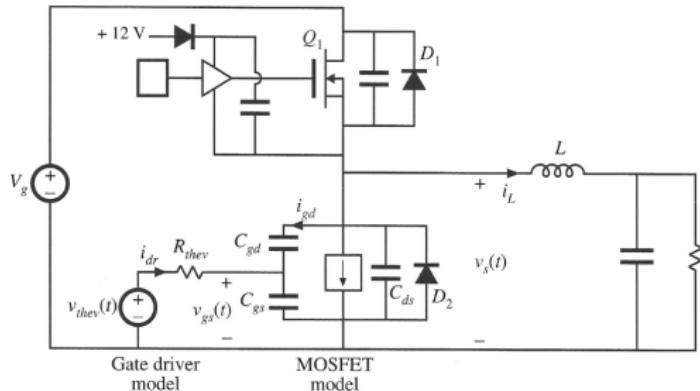

# MOSFET drivers model

Figure from [4]

- ▶ Driver is modelled by its equivalent Thevenin circuit.

- ▶ MOSFET is modelled by its equivalent dynamic equivalent circuit (see MOSFET dynamic equivalent circuit).

- ▶ Switching time can be determined with this model.

- ▶ Then, switching loss can be evaluated.

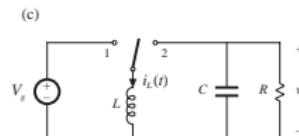

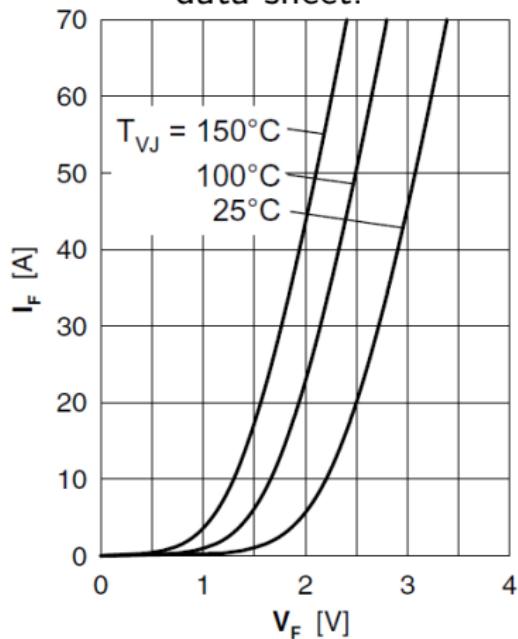

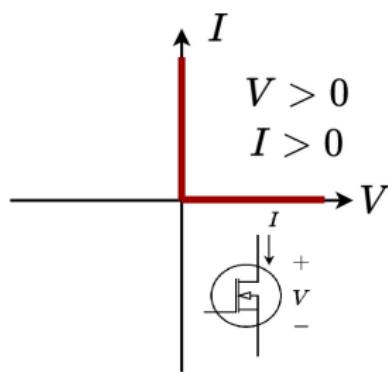

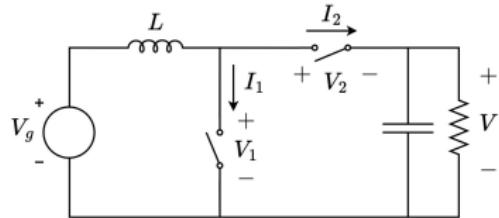

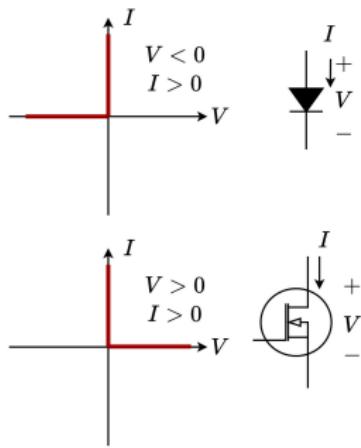

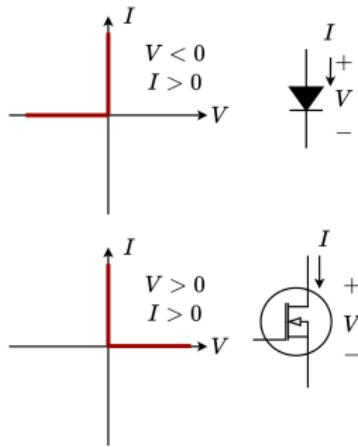

# Switch selection: controlled switch or diode?

We consider  $I > 0$  :

- ▶ if  $V > 0 \Rightarrow$  controlled switch (MOSFET, IGBT, SiC MOSFET or GaN FET)

- ▶ if  $V < 0 \Rightarrow$  diode (including controlled switch body diode)

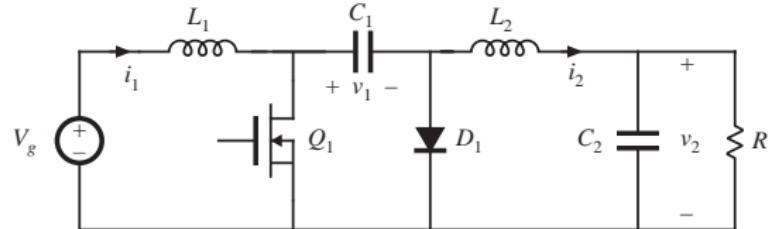

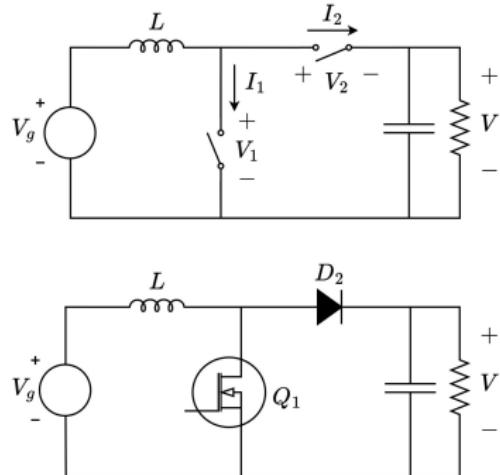

# Switch selection: controlled switch or diode?

Another example: CUK converter

We consider  $I > 0$  :

- ▶ if  $V > 0 \Rightarrow$  controlled switch (MOSFET, IGBT, SiC MOSFET or GaN FET)

- ▶ if  $V < 0 \Rightarrow$  diode (including controlled switch body diode)

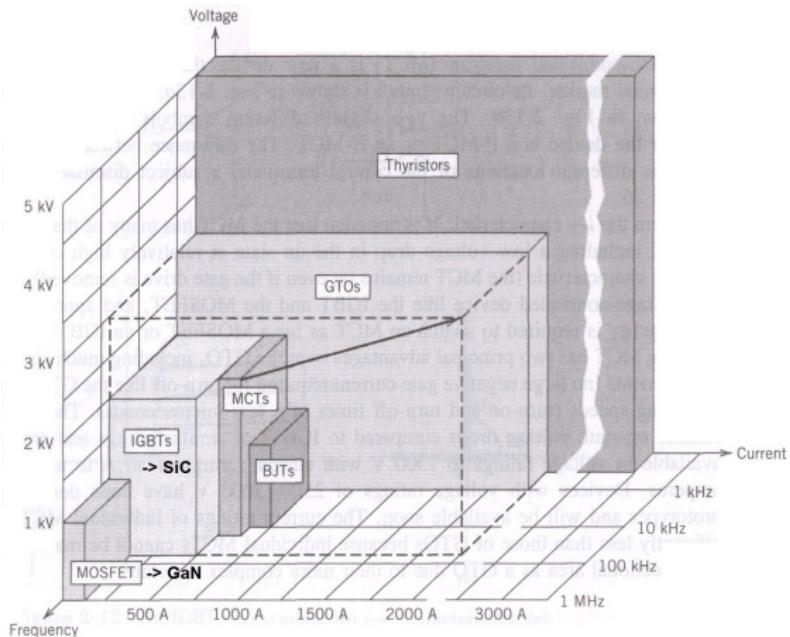

# Other power semi-conductors

Excerpt of [6]:

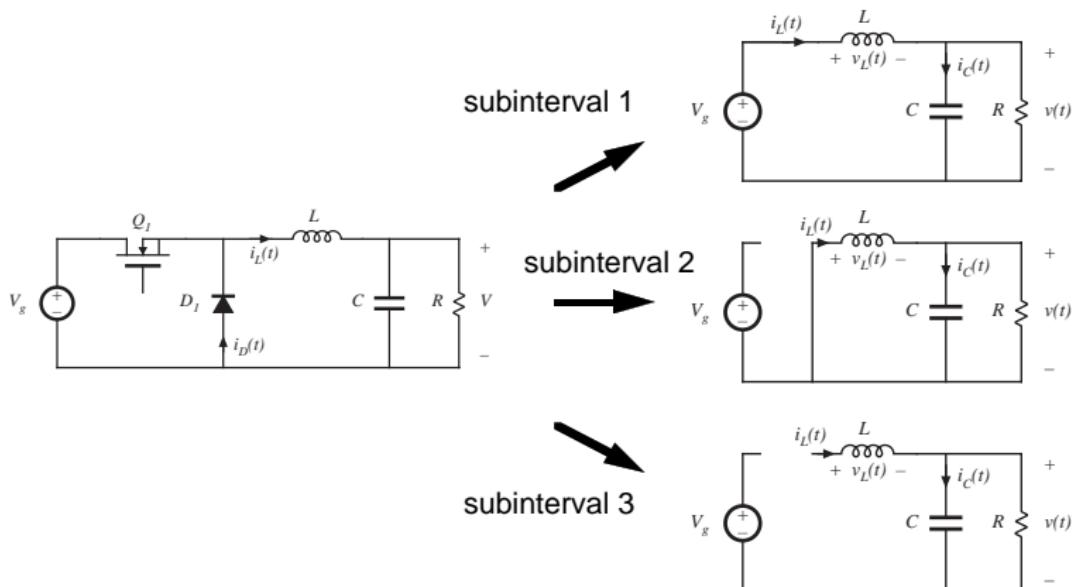

# Chapter 5: The Discontinuous Conduction Mode

- ▶ Introduction to Discontinuous Conduction Mode (DCM)

- ▶ 5.1 Origin of the discontinuous conduction mode, and mode boundary

- ▶ 5.2 Analysis of the conversion ratio  $M(D, K)$

- ▶ 5.3 Boost converter example

- ▶ Summary of results and key points

# Introduction to Discontinuous Conduction Mode (DCM)

---

- Occurs because switching ripple in inductor current or capacitor voltage causes polarity of applied switch current or voltage to reverse, such that the current- or voltage-unidirectional assumptions made in realizing the switch are violated.

- Commonly occurs in dc-dc converters and rectifiers, having single-quadrant switches. May also occur in converters having two-quadrant switches.

- Typical example: dc-dc converter operating at light load (small load current). Sometimes, dc-dc converters and rectifiers are purposely designed to operate in DCM at all loads.

- Properties of converters change radically when DCM is entered:

- $M$  becomes load-dependent

- Output impedance is increased

- Dynamics are altered

- Control of output voltage may be lost when load is removed

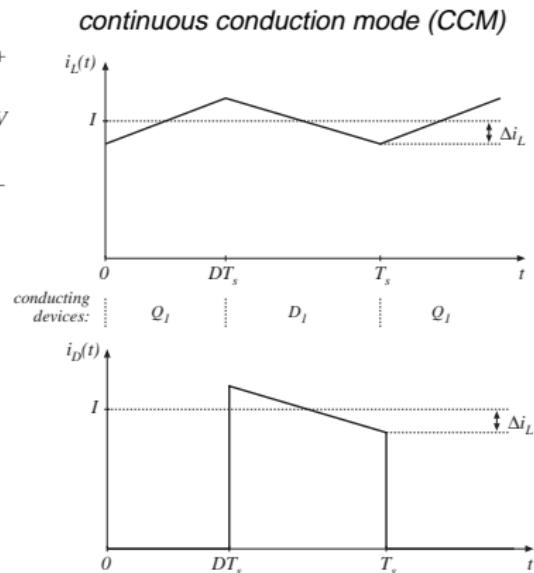

## 5.1. Origin of the discontinuous conduction mode, and mode boundary

Buck converter example, with single-quadrant switches

Minimum diode current is  $(I - \Delta i_L)$

Dc component  $I = V/R$

Current ripple is

$$\Delta i_L = \frac{(V_g - V)}{2L} DT_s = \frac{V_g DDT_s}{2L}$$

Note that  $I$  depends on load, but  $\Delta i_L$  does not.

## Reduction of load current

Increase  $R$ , until  $I = \Delta i_I$

Minimum diode current is  $(I - \Delta i_r)$

Dc component  $I = V/R$

Current ripple is

$$\Delta i_L = \frac{(V_g - V)}{2L} DT_s = \frac{V_g DD'T_s}{2L}$$

Note that  $I$  depends on load, but  $\Delta i_L$  does not.

### *CCM-DCM boundary*

conducting devices:  $Q_1$   $D_1$   $Q$

# Further reduce load current

Increase  $R$  some more, such that  $I < \Delta i_L$

Minimum diode current is  $(I - \Delta i_L)$

Dc component  $I = V/R$

Current ripple is

$$\Delta i_L = \frac{(V_g - V)}{2L} DT_s = \frac{V_g DD'T_s}{2L}$$

Note that  $I$  depends on load, but  $\Delta i_L$  does not.

The load current continues to be positive and non-zero.

*Discontinuous conduction mode*

# Mode boundary

---

$I > \Delta i_L$  for CCM

$I < \Delta i_L$  for DCM

Insert buck converter expressions for  $I$  and  $\Delta i_L$ :

$$\frac{DV_g}{R} < \frac{DD'T_s V_g}{2L}$$

Simplify:

$$\frac{2L}{RT_s} < D'$$

This expression is of the form

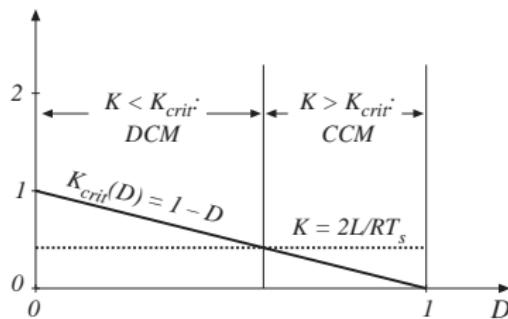

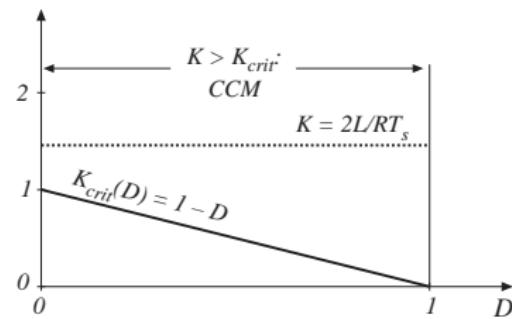

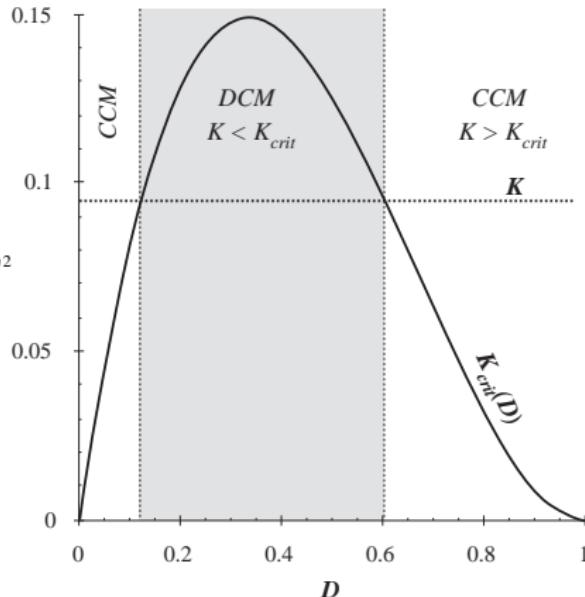

$K < K_{crit}(D)$  for DCM

where  $K = \frac{2L}{RT_s}$  and  $K_{crit}(D) = D'$

# $K$ and $K_{crit}$ vs. $D$

for  $K < 1$ :

for  $K > 1$ :

# Critical load resistance $R_{crit}$

---

---

Solve  $K_{crit}$  equation for load resistance  $R$ :

$$R < R_{crit}(D) \quad \text{for CCM}$$

$$R > R_{crit}(D) \quad \text{for DCM}$$

where  $R_{crit}(D) = \frac{2L}{D'T_s}$

# Summary: mode boundary

$$\begin{array}{lll} K > K_{crit}(D) & \text{or} & R < R_{crit}(D) \quad \text{for CCM} \\ K < K_{crit}(D) & \text{or} & R > R_{crit}(D) \quad \text{for DCM} \end{array}$$

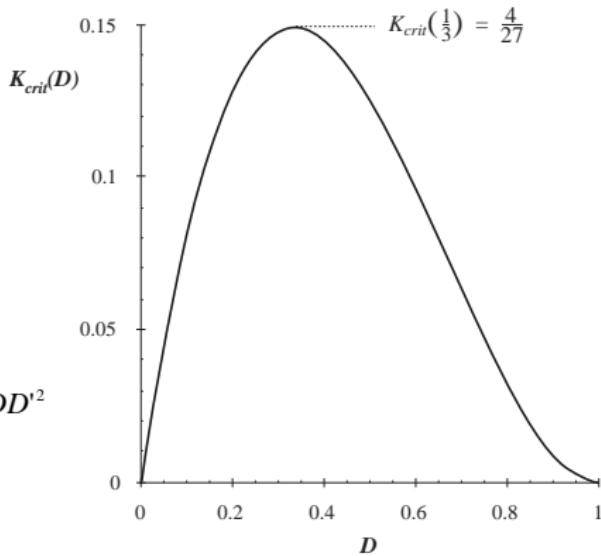

Table 5.1. CCM-DCM mode boundaries for the buck, boost, and buck-boost converters

| Converter  | $K_{crit}(D)$ | $\max_{0 \leq D \leq 1} (K_{crit})$ | $R_{crit}(D)$                | $\min_{0 \leq D \leq 1} (R_{crit})$ |

|------------|---------------|-------------------------------------|------------------------------|-------------------------------------|

| Buck       | $(1 - D)$     | 1                                   | $\frac{2L}{(1 - D)T_s}$      | $2 \frac{L}{T_s}$                   |

| Boost      | $D (1 - D)^2$ | $\frac{4}{27}$                      | $\frac{2L}{D (1 - D)^2 T_s}$ | $\frac{27}{2} \frac{L}{T_s}$        |

| Buck-boost | $(1 - D)^2$   | 1                                   | $\frac{2L}{(1 - D)^2 T_s}$   | $2 \frac{L}{T_s}$                   |

## 5.2. Analysis of the conversion ratio $M(D,K)$

---

Analysis techniques for the discontinuous conduction mode:

Inductor volt-second balance

$$\langle v_L \rangle = \frac{1}{T_s} \int_0^{T_s} v_L(t) dt = 0$$

Capacitor charge balance

$$\langle i_C \rangle = \frac{1}{T_s} \int_0^{T_s} i_C(t) dt = 0$$

Small ripple approximation sometimes applies:

$$v(t) \approx V \quad \text{because} \quad \Delta v \ll V$$

$$i(t) \approx I \quad \text{is a poor approximation when} \quad \Delta i > I$$

Converter steady-state equations obtained via charge balance on each capacitor and volt-second balance on each inductor. Use care in applying small ripple approximation.

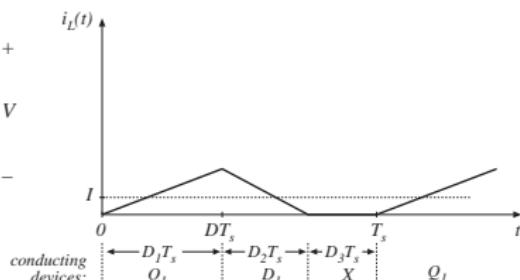

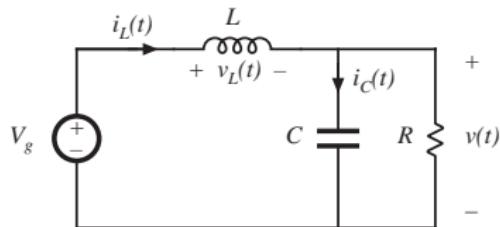

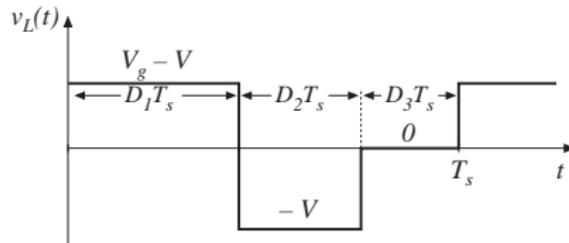

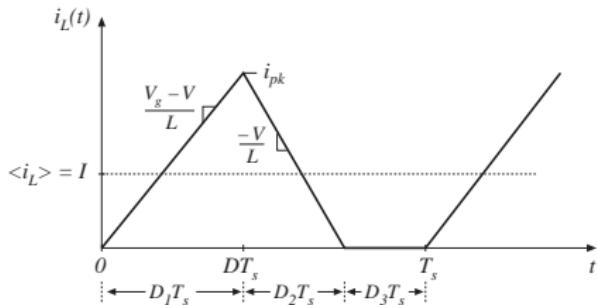

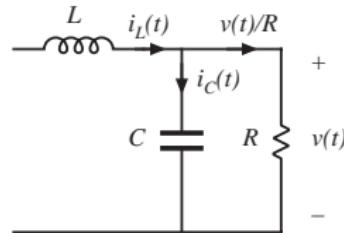

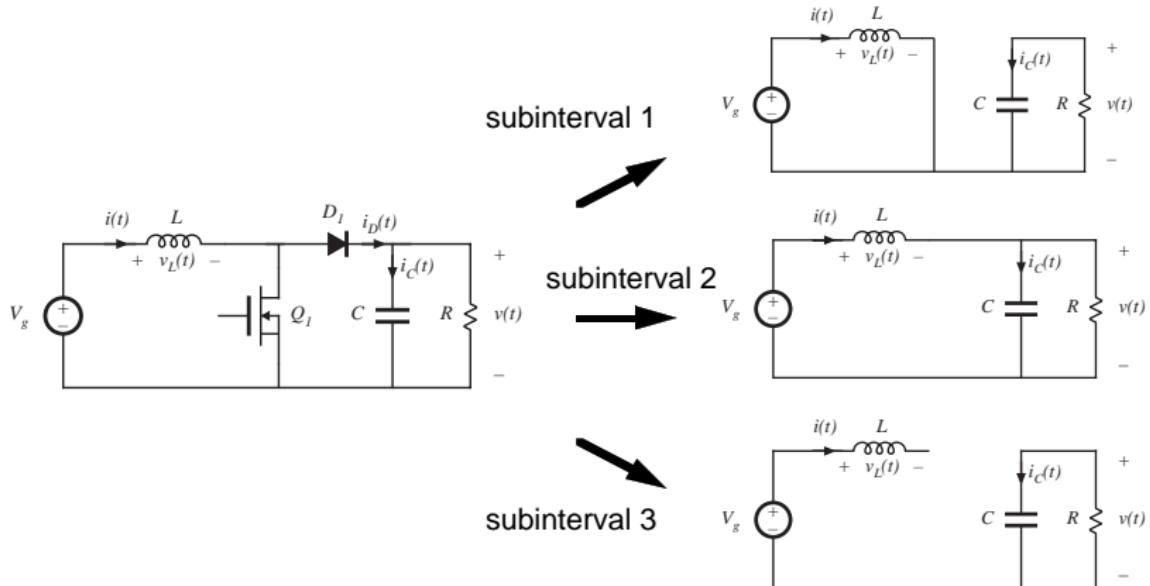

# Example: Analysis of DCM buck converter $M(D,K)$

# Subinterval 1

$$v_L(t) = V_g - v(t)$$

$$i_C(t) = i_L(t) - v(t) / R$$

Small ripple approximation

for  $v(t)$  (but not for  $i(t)$ !):

$$v_L(t) \approx V_g - V$$

$$i_C(t) \approx i_L(t) - V / R$$

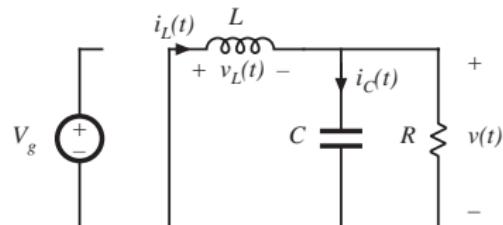

## Subinterval 2

$$v_L(t) = -v(t)$$

$$i_C(t) = i_L(t) - v(t) / R$$

Small ripple approximation

for  $v(t)$  but not for  $i(t)$ :

$$v_L(t) \approx -V$$

$$i_C(t) \approx i_L(t) - V / R$$

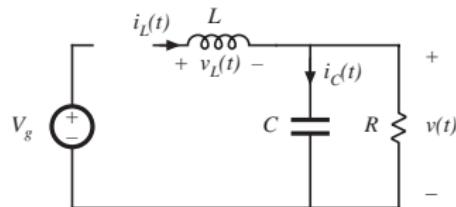

## Subinterval 3

$$v_L = 0, \quad i_L = 0$$

$$i_C(t) = i_L(t) - v(t) / R$$

Small ripple approximation:

$$v_L(t) = 0$$

$$i_C(t) = -V / R$$

# Inductor volt-second balance

Volt-second balance:

$$\langle v_L(t) \rangle = D_1(V_g - V) + D_2(-V) + D_3(0) = 0$$

Solve for  $V$ :

$$V = V_g \frac{D_1}{D_1 + D_2}$$

note that  $D_2$  is unknown

# Capacitor charge balance

node equation:

$$i_L(t) = i_C(t) + V / R$$

capacitor charge balance:

$$\langle i_C \rangle = 0$$

hence

$$\langle i_L \rangle = V / R$$

must compute dc component of inductor current and equate to load current (for this buck converter example)

# Inductor current waveform

peak current:

$$i_L(D_1 T_s) = i_{pk} = \frac{V_g - V}{L} D_1 T_s$$

average current:

$$\langle i_L \rangle = \frac{1}{T_s} \int_0^{T_s} i_L(t) dt$$

triangle area formula:

$$\int_0^{T_s} i_L(t) dt = \frac{1}{2} i_{pk} (D_1 + D_2) T_s$$

$$\langle i_L \rangle = (V_g - V) \frac{D_1 T_s}{2L} (D_1 + D_2)$$

equate dc component to dc load current:

$$\frac{V}{R} = \frac{D_1 T_s}{2L} (D_1 + D_2) (V_g - V)$$

# Solution for $V$

---

Two equations and two unknowns ( $V$  and  $D_2$ ):

$$V = V_g \frac{D_1}{D_1 + D_2} \quad \text{(from inductor volt-second balance)}$$

$$\frac{V}{R} = \frac{D_1 T_s}{2L} (D_1 + D_2) (V_g - V) \quad \text{(from capacitor charge balance)}$$

Eliminate  $D_2$ , solve for  $V$ :

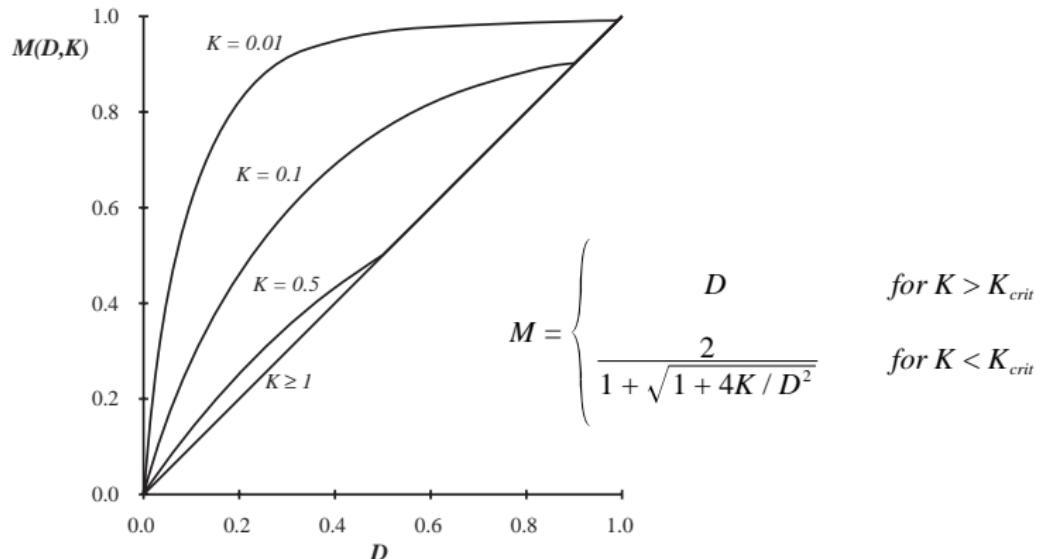

$$\frac{V}{V_g} = \frac{2}{1 + \sqrt{1 + 4K / D_1^2}}$$

where  $K = 2L / RT_s$

valid for  $K < K_{crit}$

## Buck converter $M(D, K)$

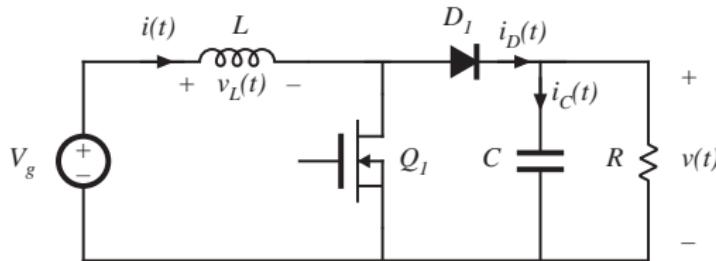

## 5.3. Boost converter example

Mode boundary:

$$\begin{aligned} I > \Delta i_L & \text{ for CCM} \\ I < \Delta i_L & \text{ for DCM} \end{aligned}$$

Previous CCM soln:

$$I = \frac{V_g}{D^2 R} \quad \Delta i_L = \frac{V_g}{2L} DT_s$$

# Mode boundary

$$\frac{V_g}{D'^2 R} > \frac{DT_s V_g}{2L} \quad \text{for CCM}$$

$$\frac{2L}{RT_s} > DD'^2 \quad \text{for CCM}$$

$K > K_{crit}(D)$  for CCM

$K < K_{crit}(D)$  for DCM

where  $K = \frac{2L}{RT_s}$  and  $K_{crit}(D) = DD'^2$

# Mode boundary

$K > K_{crit}(D)$  for CCM

$K < K_{crit}(D)$  for DCM

where  $K = \frac{2L}{RT_s}$  and  $K_{crit}(D) = DD'^2$

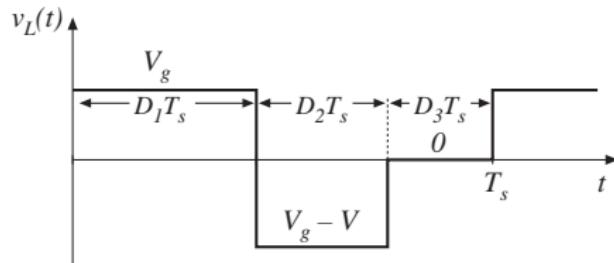

# Conversion ratio: DCM boost

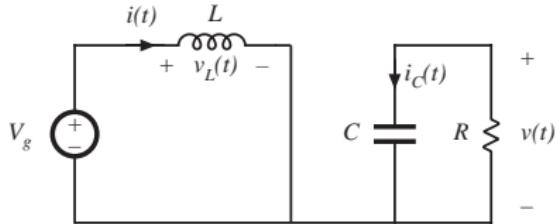

# Subinterval 1

$$v_L(t) = V_g$$

$$i_C(t) = -v(t) / R$$

Small ripple approximation

for  $v(t)$  (but not for  $i(t)$ !):

$$v_L(t) \approx V_g$$

$$i_C(t) \approx -V / R$$

$$0 < t < D_1 T_s$$

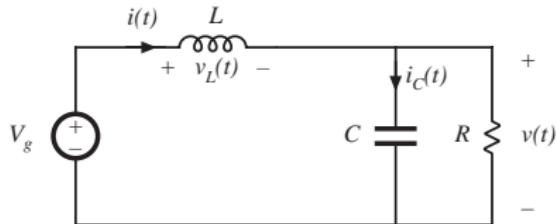

## Subinterval 2

$$v_L(t) = V_g - v(t)$$

$$i_C(t) = i(t) - v(t) / R$$

Small ripple approximation

for  $v(t)$  but not for  $i(t)$ :

$$v_L(t) \approx V_g - V$$

$$i_C(t) \approx i(t) - V / R$$

$$D_1 T_s < t < (D_1 + D_2) T_s$$

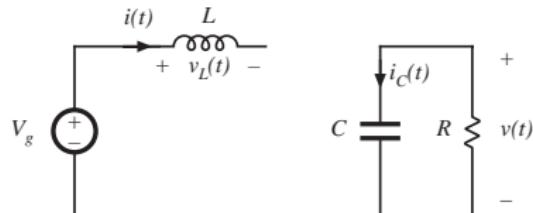

## Subinterval 3

$$v_L = 0, \quad i = 0 \\ i_C(t) = -v(t) / R$$

Small ripple approximation:

$$v_L(t) = 0 \\ i_C(t) = -V / R$$

$$(D_1 + D_2)T_s < t < T_s$$

# Inductor volt-second balance

Volt-second balance:

$$D_1 V_g + D_2 (V_g - V) + D_3(0) = 0$$

Solve for  $V$ :

$$V = \frac{D_1 + D_2}{D_2} V_g$$

note that  $D_2$  is unknown

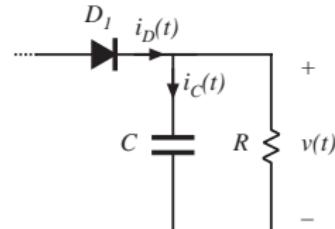

# Capacitor charge balance

node equation:

$$i_D(t) = i_C(t) + v(t) / R$$

capacitor charge balance:

$$\langle i_C \rangle = 0$$

hence

$$\langle i_D \rangle = V / R$$

must compute dc component of diode current and equate to load current (for this boost converter example)

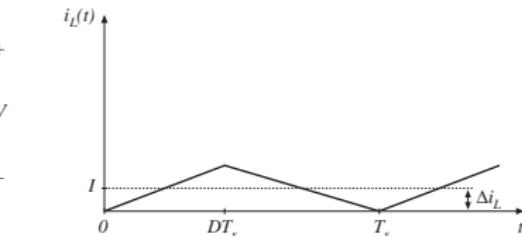

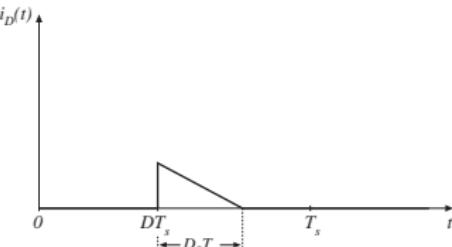

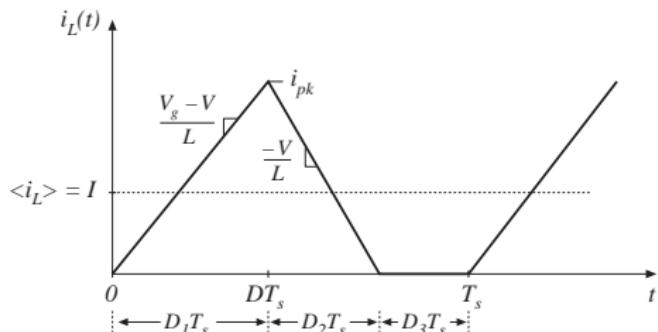

# Inductor and diode current waveforms

peak current:

$$i_{pk} = \frac{V_g}{L} D_1 T_s$$

average diode current:

$$\langle i_D \rangle = \frac{1}{T_s} \int_0^{T_s} i_D(t) dt$$

triangle area formula:

$$\int_0^{T_s} i_D(t) dt = \frac{1}{2} i_{pk} D_2 T_s$$

## Equate diode current to load current

---

---

average diode current:

$$\langle i_D \rangle = \frac{1}{T_s} \left( \frac{1}{2} i_{pk} D_2 T_s \right) = \frac{V_g D_1 D_2 T_s}{2L}$$

equate to dc load current:

$$\frac{V_g D_1 D_2 T_s}{2L} = \frac{V}{R}$$

# Solution for $V$

---

Two equations and two unknowns ( $V$  and  $D_2$ ):

$$V = \frac{D_1 + D_2}{D_2} V_g \quad \text{(from inductor volt-second balance)}$$

$$\frac{V_g D_1 D_2 T_s}{2L} = \frac{V}{R} \quad \text{(from capacitor charge balance)}$$

Eliminate  $D_2$ , solve for  $V$ . From volt-sec balance eqn:

$$D_2 = D_1 \frac{V_g}{V - V_g}$$

Substitute into charge balance eqn, rearrange terms:

$$V^2 - VV_g - \frac{V_g^2 D_1^2}{K} = 0$$

# Solution for $V$

$$V^2 - VV_g - \frac{V_g^2 D_1^2}{K} = 0$$

Use quadratic formula:

$$\frac{V}{V_g} = \frac{1 \pm \sqrt{1 + 4D_1^2 / K}}{2}$$

Note that one root leads to positive  $V$ , while other leads to negative  $V$ . Select positive root:

$$\frac{V}{V_g} = M(D_1, K) = \frac{1 + \sqrt{1 + 4D_1^2 / K}}{2}$$

where  $K = 2L / RT_s$

valid for  $K < K_{crit}(D)$

Transistor duty cycle  $D = \text{interval 1 duty cycle } D_1$

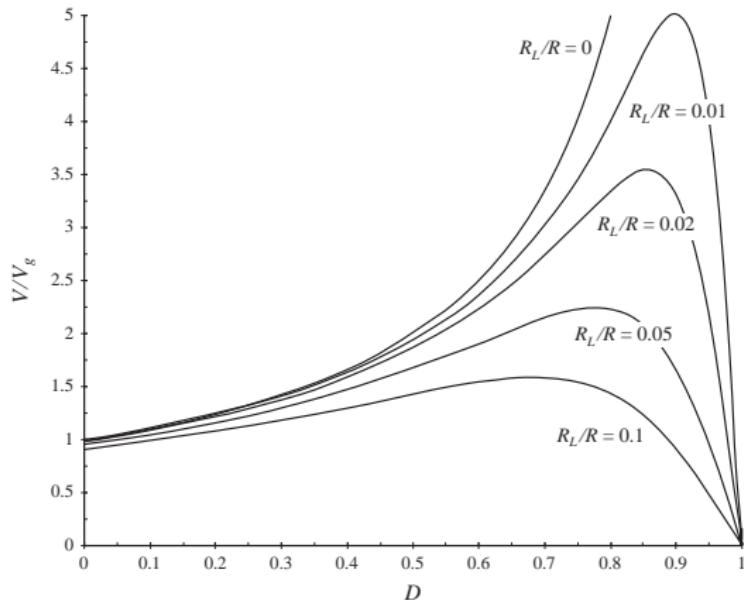

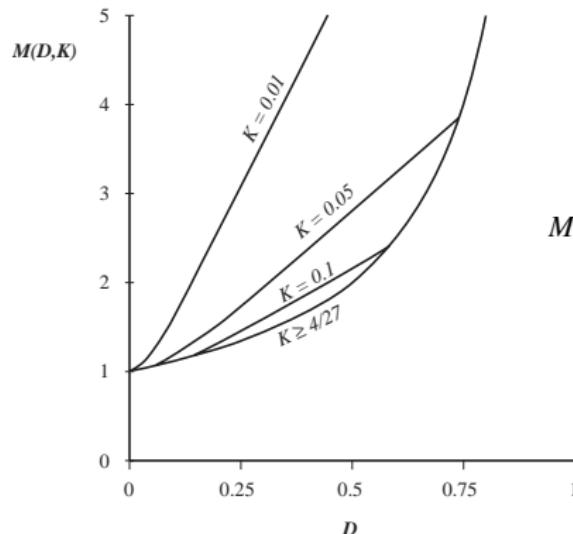

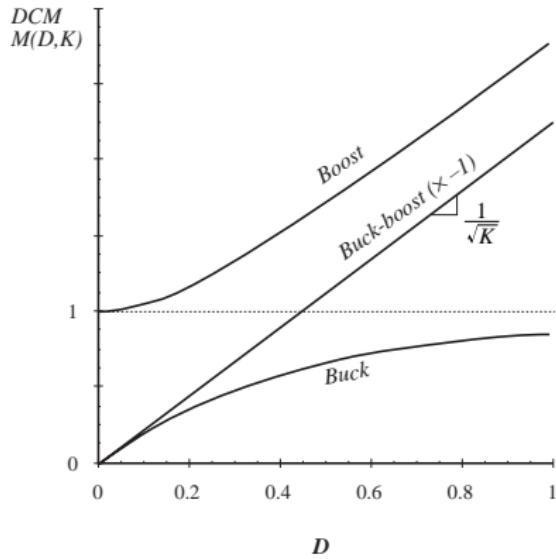

# Boost converter characteristics

$$M = \begin{cases} \frac{1}{1-D} & \text{for } K > K_{crit} \\ \frac{1 + \sqrt{1 + 4D^2 / K}}{2} & \text{for } K < K_{crit} \end{cases}$$

Approximate  $M$  in DCM:

$$M \approx \frac{1}{2} + \frac{D}{\sqrt{K}}$$

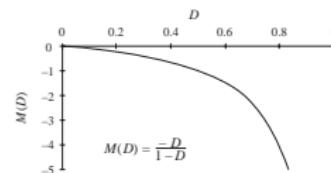

# Summary of DCM characteristics

Table 5.2. Summary of CCM-DCM characteristics for the buck, boost, and buck-boost converters

| Converter  | $K_{crit}(D)$ | $DCM\ M(D,K)$                     | $DCM\ D_2(D,K)$      | $CCM\ M(D)$        |

|------------|---------------|-----------------------------------|----------------------|--------------------|

| Buck       | $(1 - D)$     | $\frac{2}{1 + \sqrt{1 + 4K/D^2}}$ | $\frac{K}{D} M(D,K)$ | $D$                |

| Boost      | $D(1 - D)^2$  | $\frac{1 + \sqrt{1 + 4D^2/K}}{2}$ | $\frac{K}{D} M(D,K)$ | $\frac{1}{1 - D}$  |

| Buck-boost | $(1 - D)^2$   | $-\frac{D}{\sqrt{K}}$             | $\sqrt{K}$           | $-\frac{D}{1 - D}$ |

with  $K = 2L / RT_s$ ,  $DCM$  occurs for  $K < K_{crit}$ .

# Summary of DCM characteristics

- DCM buck and boost characteristics are asymptotic to  $M = 1$  and to the DCM buck-boost characteristic

- DCM buck-boost characteristic is linear

- CCM and DCM characteristics intersect at mode boundary. Actual  $M$  follows characteristic having larger magnitude

- DCM boost characteristic is nearly linear

# Summary of key points

---

---

1. The discontinuous conduction mode occurs in converters containing current- or voltage-unidirectional switches, when the inductor current or capacitor voltage ripple is large enough to cause the switch current or voltage to reverse polarity.

2. Conditions for operation in the discontinuous conduction mode can be found by determining when the inductor current or capacitor voltage ripples and dc components cause the switch on-state current or off-state voltage to reverse polarity.

3. The dc conversion ratio  $M$  of converters operating in the discontinuous conduction mode can be found by application of the principles of inductor volt-second and capacitor charge balance.

# Summary of key points

---

4. Extra care is required when applying the small-ripple approximation. Some waveforms, such as the output voltage, should have small ripple which can be neglected. Other waveforms, such as one or more inductor currents, may have large ripple that cannot be ignored.

5. The characteristics of a converter changes significantly when the converter enters DCM. The output voltage becomes load-dependent, resulting in an increase in the converter output impedance.

# Chapter 13: Basic Magnetics Theory

- ▶ Inductor example

- ▶ 13.1.2 Magnetic circuits

- ▶ 13.2 Transformer modeling

- ▶ 13.2.1 The ideal transformer

- ▶ 13.2.2 The magnetizing inductance

- ▶ 13.2.3 Leakage inductances

- ▶ 13.3 Loss mechanisms in magnetic devices

- ▶ 13.3.1 Core loss

- ▶ 13.3.2 Low-frequency copper loss

- ▶ 13.4 Eddy currents in winding conductors

- ▶ 13.4.1 Intro to the skin and proximity effects

- ▶ Discussion: design of winding geometry to minimize proximity loss

- ▶ Litz wire

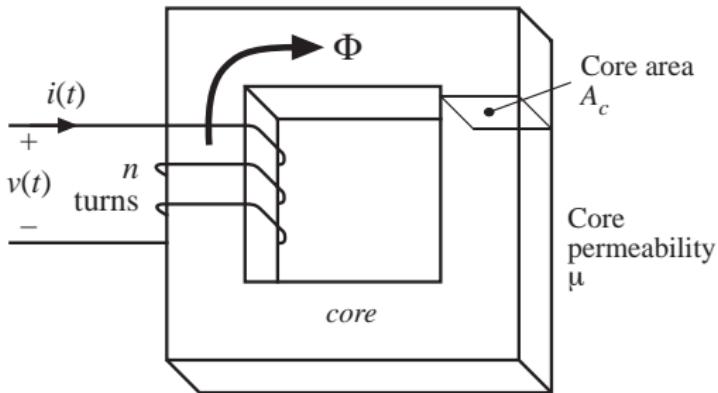

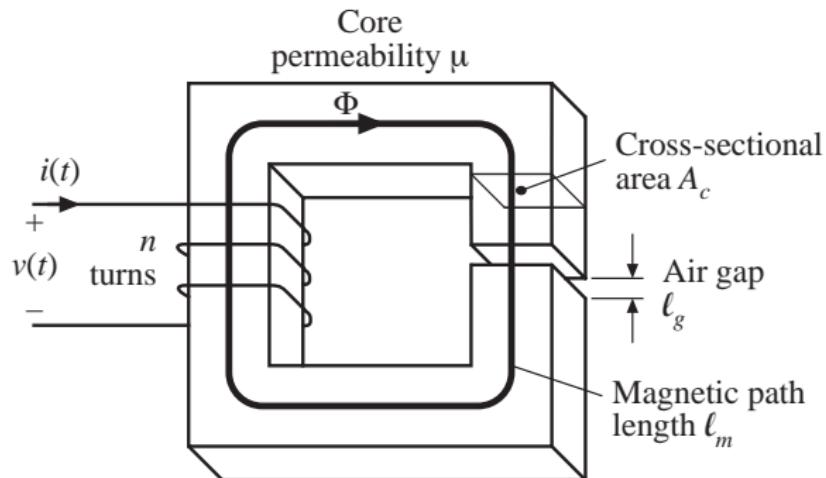

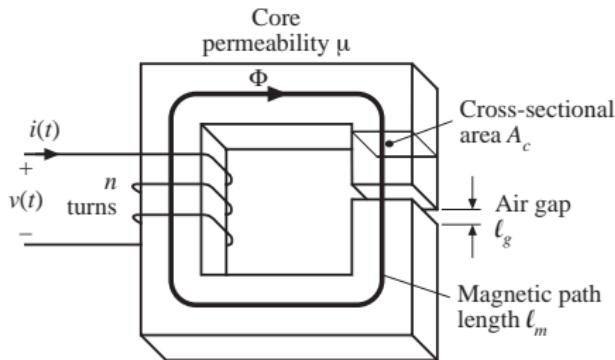

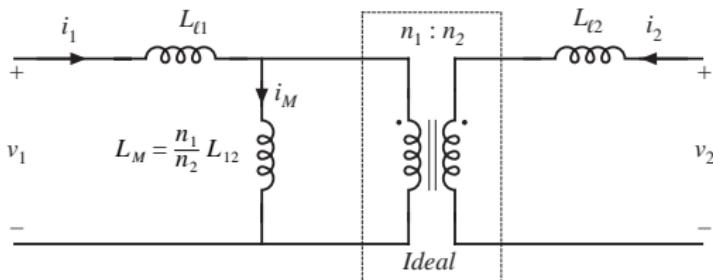

## Example: a simple inductor

*Faraday's law:*

For each turn of wire, we can write

$$v_{turn}(t) = \frac{d\Phi(t)}{dt}$$

Total winding voltage is

$$v(t) = nv_{turn}(t) = n \frac{d\Phi(t)}{dt}$$

Express in terms of the average flux density  $B(t) = \mathcal{F}(t)/A_c$

$$v(t) = nA_c \frac{dB(t)}{dt}$$

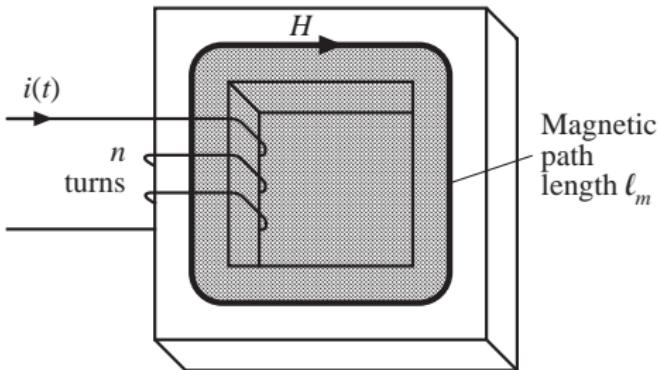

## Inductor example: Ampere's law

Choose a closed path which follows the average magnetic field line around the interior of the core. Length of this path is called the *mean magnetic path length*  $\ell_m$ .

For uniform field strength  $H(t)$ , the core MMF around the path is  $H \ell_m$ .

Winding contains  $n$  turns of wire, each carrying current  $i(t)$ . The net current passing through the path interior (i.e., through the core window) is  $ni(t)$ .

From Ampere's law, we have

$$H(t) \ell_m = n i(t)$$

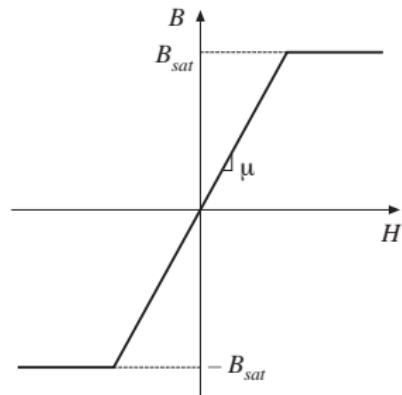

## Inductor example: core material model

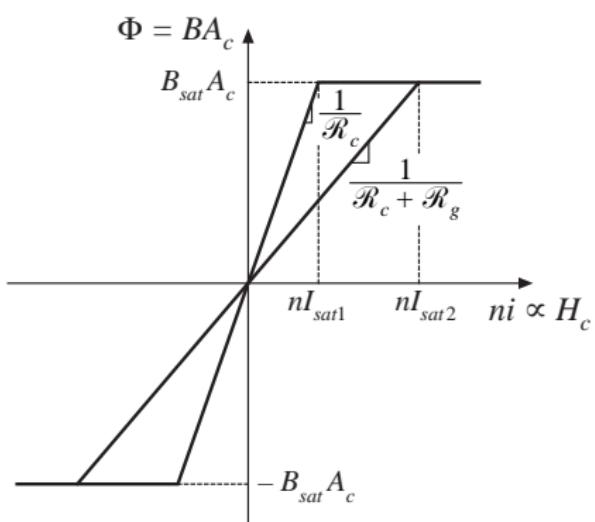

$$B = \begin{cases} B_{sat} & \text{for } H \geq B_{sat}/\mu \\ \mu H & \text{for } |H| < B_{sat}/\mu \\ -B_{sat} & \text{for } H \leq -B_{sat}/\mu \end{cases}$$

Find winding current at onset of saturation:

substitute  $i = I_{sat}$  and  $H = B_{sat}/\mu$  into

equation previously derived via Ampere's

law. Result is

$$I_{sat} = \frac{B_{sat}\ell_m}{\mu n}$$

# Electrical terminal characteristics

We have:

$$v(t) = nA_c \frac{dB(t)}{dt} \quad H(t) \ell_m = n i(t) \quad B = \begin{cases} B_{sat} & \text{for } H \geq B_{sat}/\mu \\ \mu H & \text{for } |H| < B_{sat}/\mu \\ -B_{sat} & \text{for } H \leq -B_{sat}/\mu \end{cases}$$

Eliminate  $B$  and  $H$ , and solve for relation between  $v$  and  $i$ . For  $|i| < I_{sat}$ ,

$$v(t) = \mu n A_c \frac{dH(t)}{dt} \quad \longrightarrow \quad v(t) = \frac{\mu n^2 A_c}{\ell_m} \frac{di(t)}{dt}$$

which is of the form

$$v(t) = L \frac{di(t)}{dt} \quad \text{with} \quad L = \frac{\mu n^2 A_c}{\ell_m}$$

—an inductor

For  $|i| > I_{sat}$  the flux density is constant and equal to  $B_{sat}$ . Faraday's law then predicts

$$v(t) = nA_c \frac{dB_{sat}}{dt} = 0 \quad \text{—saturation leads to short circuit}$$

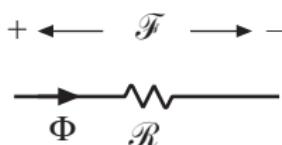

## 13.1.2 Magnetic circuits

Uniform flux and magnetic field inside a rectangular element:

MMF between ends of element is

$$\mathcal{F} = H\ell$$

Since  $H = B / \mu$  and  $B = \Phi / A_c$ , we can express  $\mathcal{F}$  as

$$\mathcal{F} = \Phi \mathcal{R}$$

with

$$\mathcal{R} = \frac{\ell}{\mu A_c}$$

A corresponding model:

$\mathcal{R}$  = reluctance of element

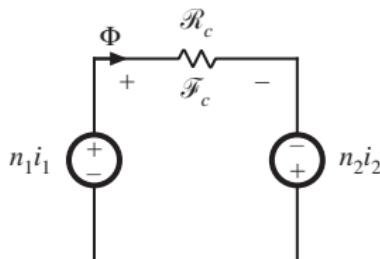

## Magnetic circuits: magnetic structures composed of multiple windings and heterogeneous elements

---

- Represent each element with reluctance

- Windings are sources of MMF

- MMF → voltage, flux → current

- Solve magnetic circuit using Kirchoff's laws, etc.

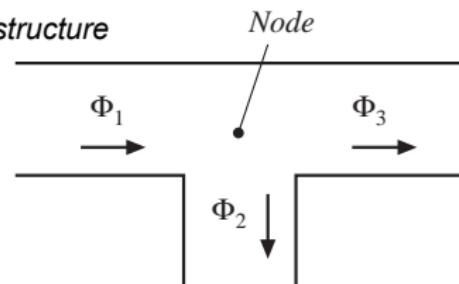

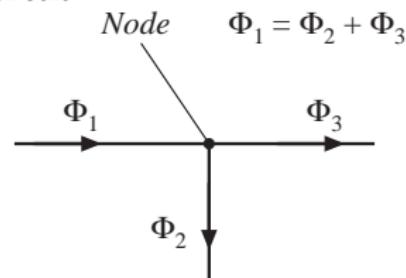

## Magnetic analog of Kirchoff's current law

Divergence of  $B = 0$

Flux lines are continuous and cannot end

Total flux entering a node must be zero

*Physical structure*

*Magnetic circuit*

# Magnetic analog of Kirchoff's voltage law

---

Follows from Ampere's law:

$$\oint_{closed\ path} \mathbf{H} \cdot d\ell = \text{total current passing through interior of path}$$

Left-hand side: sum of MMF's across the reluctances around the closed path

Right-hand side: currents in windings are sources of MMF's. An  $n$ -turn winding carrying current  $i(t)$  is modeled as an MMF (voltage) source, of value  $ni(t)$ .

Total MMF's around the closed path add up to zero.

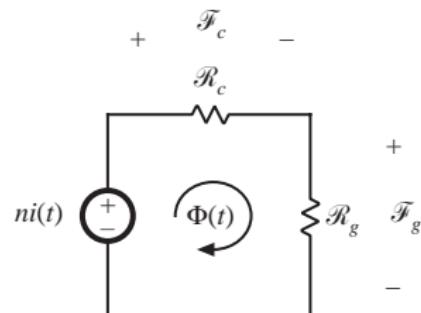

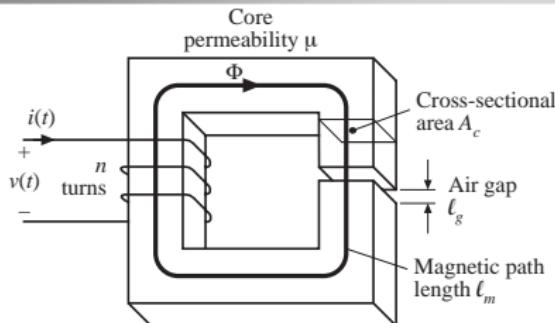

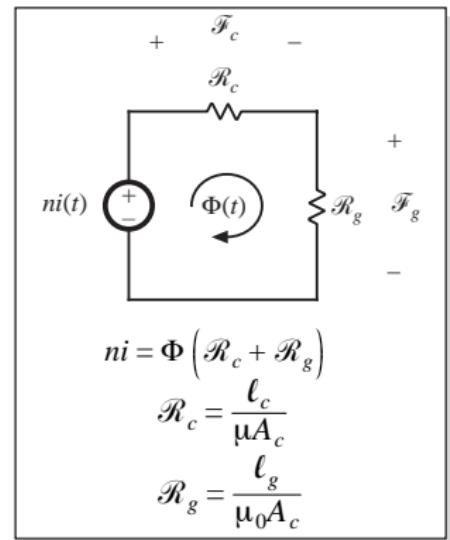

## Example: inductor with air gap

# Magnetic circuit model

$$\mathcal{F}_c + \mathcal{F}_g = ni$$

$$\mathcal{R}_c = \frac{\ell_c}{\mu A_c}$$

$$ni = \Phi \left( \mathcal{R}_c + \mathcal{R}_g \right)$$

$$\mathcal{R}_g = \frac{\ell_g}{\mu_0 A_c}$$

# Solution of model

Faraday's law:  $v(t) = n \frac{d\Phi(t)}{dt}$

Substitute for  $\Phi$ :  $v(t) = \frac{n^2}{\mathcal{R}_c + \mathcal{R}_g} \frac{di(t)}{dt}$

Hence inductance is

$$L = \frac{n^2}{\mathcal{R}_c + \mathcal{R}_g}$$

$$ni = \Phi (\mathcal{R}_c + \mathcal{R}_g)$$

$$\mathcal{R}_c = \frac{\ell_c}{\mu A_c}$$

$$\mathcal{R}_g = \frac{\ell_g}{\mu_0 A_c}$$

# Effect of air gap

$$ni = \Phi (\mathcal{R}_c + \mathcal{R}_g)$$

$$L = \frac{n^2}{\mathcal{R}_c + \mathcal{R}_g}$$

$$\Phi_{sat} = B_{sat} A_c$$

$$I_{sat} = \frac{B_{sat} A_c}{n} (\mathcal{R}_c + \mathcal{R}_g)$$

Effect of air gap:

- decrease inductance

- increase saturation current

- inductance is less dependent on core permeability

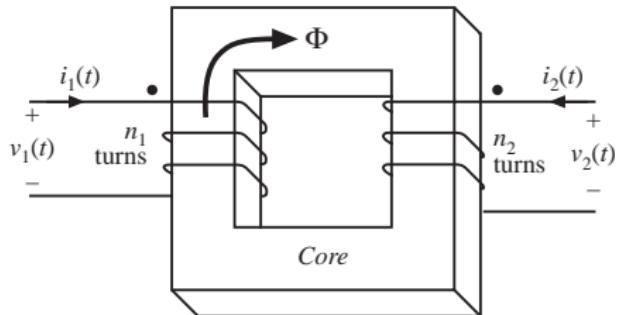

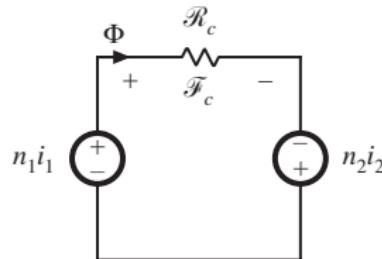

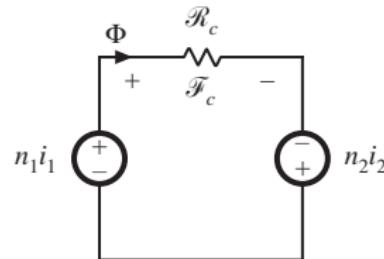

## 13.2 Transformer modeling

Two windings, no air gap:

$$\mathcal{R} = \frac{\ell_m}{\mu A_c}$$

$$\mathcal{F}_c = n_1 i_1 + n_2 i_2$$

$$\Phi \mathcal{R} = n_1 i_1 + n_2 i_2$$

Magnetic circuit model:

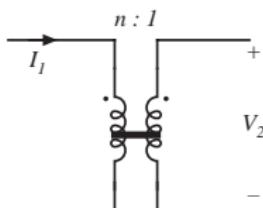

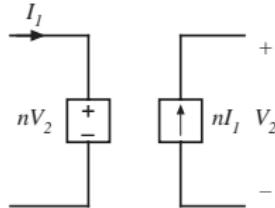

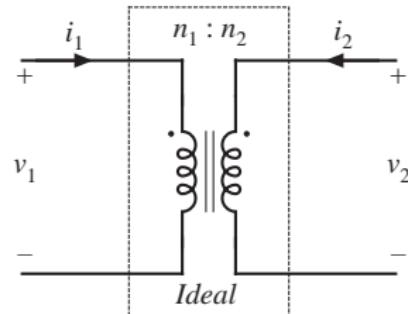

## 13.2.1 The ideal transformer

In the ideal transformer, the core reluctance  $\mathcal{R}$  approaches zero.

MMF  $\mathcal{F}_c = \Phi \mathcal{R}$  also approaches zero. We then obtain

$$0 = n_1 i_1 + n_2 i_2$$

Also, by Faraday's law,

$$v_1 = n_1 \frac{d\Phi}{dt}$$

$$v_2 = n_2 \frac{d\Phi}{dt}$$

Eliminate  $\Phi$ :

$$\frac{d\Phi}{dt} = \frac{v_1}{n_1} = \frac{v_2}{n_2}$$

Ideal transformer equations:

$$\frac{v_1}{n_1} = \frac{v_2}{n_2} \quad \text{and} \quad n_1 i_1 + n_2 i_2 = 0$$

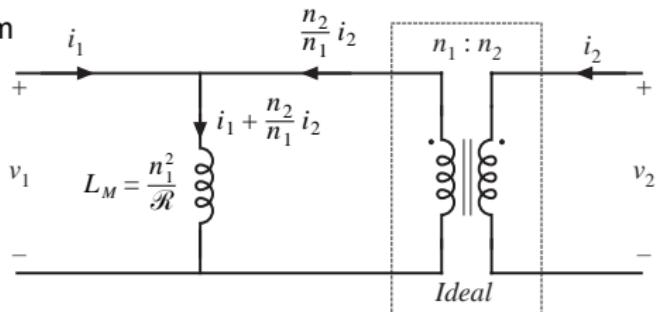

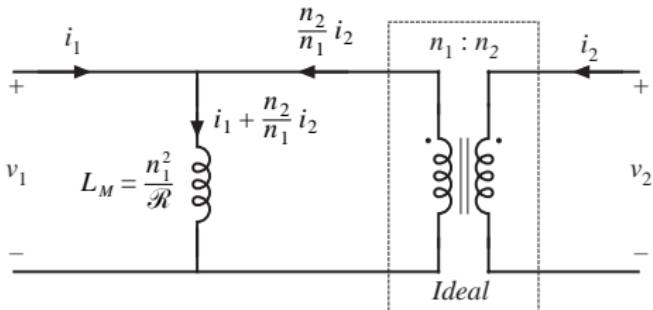

## 13.2.2 The magnetizing inductance

For nonzero core reluctance, we obtain

$$\Phi \mathcal{R} = n_1 i_1 + n_2 i_2 \quad \text{with} \quad v_1 = n_1 \frac{d\Phi}{dt}$$

Eliminate  $\Phi$ :

$$v_1 = \frac{n_1^2}{\mathcal{R}} \frac{d}{dt} \left[ i_1 + \frac{n_2}{n_1} i_2 \right]$$

This equation is of the form

$$v_1 = L_M \frac{di_M}{dt}$$

with

$$L_M = \frac{n_1^2}{\mathcal{R}}$$

$$i_M = i_1 + \frac{n_2}{n_1} i_2$$

# Magnetizing inductance: discussion

---

- Models magnetization of core material

- A real, physical inductor, that exhibits saturation and hysteresis

- If the secondary winding is disconnected:

- we are left with the primary winding on the core

- primary winding then behaves as an inductor

- the resulting inductor is the magnetizing inductance, referred to the primary winding

- Magnetizing current causes the ratio of winding currents to differ from the turns ratio

## Transformer saturation

---

- Saturation occurs when core flux density  $B(t)$  exceeds saturation flux density  $B_{sat}$ .

- When core saturates, the magnetizing current becomes large, the impedance of the magnetizing inductance becomes small, and the windings are effectively shorted out.

- Large winding currents  $i_1(t)$  and  $i_2(t)$  **do not** necessarily lead to saturation. If

$$0 = n_1 i_1 + n_2 i_2$$

then the magnetizing current is zero, and there is no net magnetization of the core.

- Saturation is caused by excessive applied volt-seconds

## Saturation vs. applied volt-seconds

Magnetizing current depends on the integral of the applied winding voltage:

$$i_M(t) = \frac{1}{L_M} \int v_1(t) dt$$

Flux density is proportional:

$$B(t) = \frac{1}{n_1 A_c} \int v_1(t) dt$$

Flux density becomes large, and core saturates, when the applied volt-seconds  $\lambda_1$  are too large, where

$$\lambda_1 = \int_{t_1}^{t_2} v_1(t) dt$$

limits of integration chosen to coincide with positive portion of applied voltage waveform

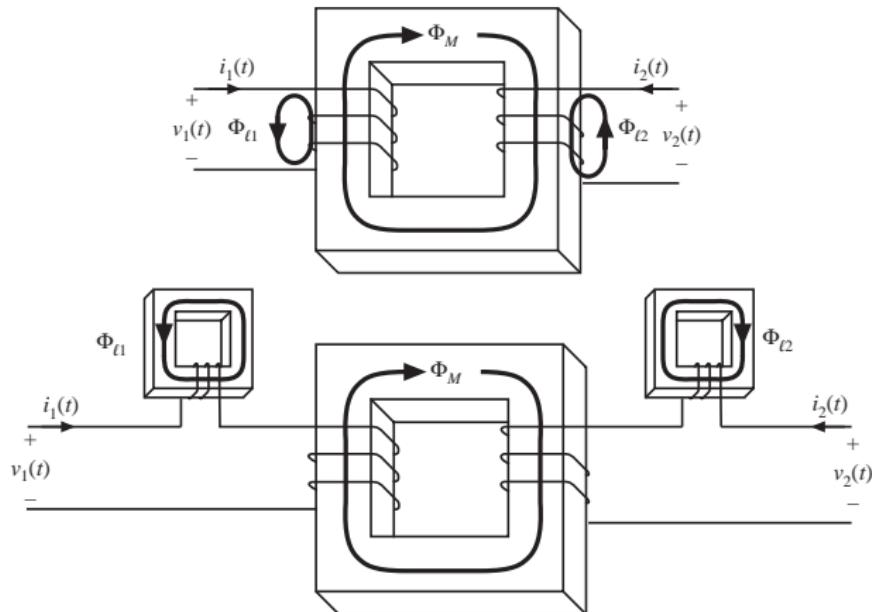

### 13.2.3 Leakage inductances

## Transformer model, including leakage inductance

Terminal equations can be written in the form

$$\begin{bmatrix} v_1(t) \\ v_2(t) \end{bmatrix} = \begin{bmatrix} L_{11} & L_{12} \\ L_{12} & L_{22} \end{bmatrix} \frac{d}{dt} \begin{bmatrix} i_1(t) \\ i_2(t) \end{bmatrix}$$

mutual inductance:

$$L_{12} = \frac{n_1 n_2}{\mathcal{R}} = \frac{n_2}{n_1} L_M$$

primary and secondary self-inductances:

$$L_{11} = L_{\ell 1} + \frac{n_1}{n_2} L_{12}$$

$$L_{22} = L_{\ell 2} + \frac{n_2}{n_1} L_{12}$$

effective turns ratio  $n_e = \sqrt{\frac{L_{22}}{L_{11}}}$

coupling coefficient  $k = \frac{L_{12}}{\sqrt{L_{11} L_{22}}}$

## 13.3 Loss mechanisms in magnetic devices

---

Low-frequency losses:

Dc copper loss

Core loss: hysteresis loss

High-frequency losses: the skin effect

Core loss: classical eddy current losses

Eddy current losses in ferrite cores

High frequency copper loss: the proximity effect

Proximity effect: high frequency limit

MMF diagrams, losses in a layer, and losses in basic multilayer windings

Effect of PWM waveform harmonics

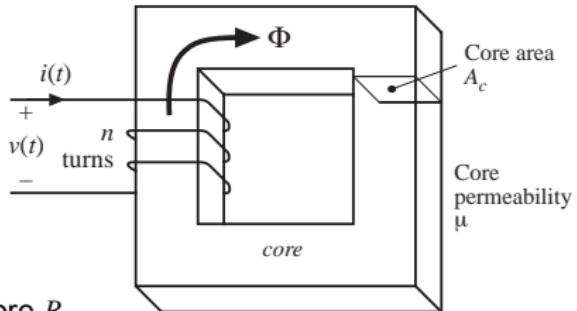

### 13.3.1 Core loss

Energy per cycle  $W$  flowing into  $n$ -turn winding of an inductor, excited by periodic waveforms of frequency  $f$ :

$$W = \int_{\text{one cycle}} v(t)i(t)dt$$

Relate winding voltage and current to core  $B$  and  $H$  via Faraday's law and Ampere's law:

$$v(t) = nA_c \frac{dB(t)}{dt} \quad H(t)\ell_m = ni(t)$$

Substitute into integral:

$$\begin{aligned} W &= \int_{\text{one cycle}} \left( nA_c \frac{dB(t)}{dt} \right) \left( \frac{H(t)\ell_m}{n} \right) dt \\ &= (A_c \ell_m) \int_{\text{one cycle}} H dB \end{aligned}$$

## Core loss: Hysteresis loss

$$W = (A_c \ell_m) \int_{\text{one cycle}} H dB$$

The term  $A_c \ell_m$  is the volume of the core, while the integral is the area of the  $B$ - $H$  loop.

(energy lost per cycle) = (core volume) (area of  $B$ - $H$  loop)

$$P_H = (f)(A_c \ell_m) \int_{\text{one cycle}} H dB$$

Hysteresis loss is directly proportional to applied frequency

# Modeling hysteresis loss

---

- Hysteresis loss varies directly with applied frequency

- Dependence on maximum flux density: how does area of  $B$ - $H$  loop depend on maximum flux density (and on applied waveforms)?

Empirical equation (Steinmetz equation):

$$P_H = K_H f B_{\max}^\alpha (\text{core volume})$$

The parameters  $K_H$  and  $\alpha$  are determined experimentally.

Dependence of  $P_H$  on  $B_{\max}$  is predicted by the theory of magnetic domains.

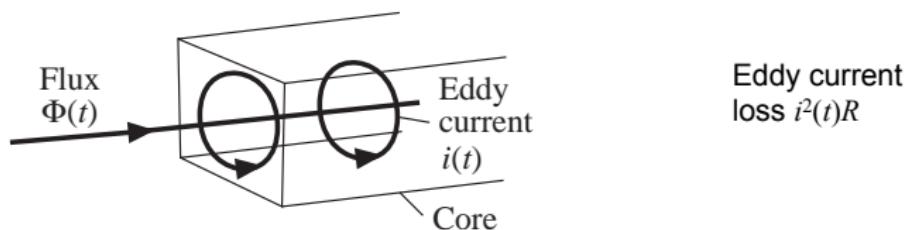

## Core loss: eddy current loss

Magnetic core materials are reasonably good conductors of electric current. Hence, according to Lenz's law, magnetic fields within the core induce currents ("eddy currents") to flow within the core. The eddy currents flow such that they tend to generate a flux which opposes changes in the core flux  $\Phi(t)$ . The eddy currents tend to prevent flux from penetrating the core.

Eddy current loss  $i^2(t)R$

# Modeling eddy current loss

- Ac flux  $\Phi(t)$  induces voltage  $v(t)$  in core, according to Faraday's law. Induced voltage is proportional to derivative of  $\Phi(t)$ . In consequence, magnitude of induced voltage is directly proportional to excitation frequency  $f$ .

- If core material impedance  $Z$  is purely resistive and independent of frequency,  $Z = R$ , then eddy current magnitude is proportional to voltage:  $i(t) = v(t)/R$ . Hence magnitude of  $i(t)$  is directly proportional to excitation frequency  $f$ .

- Eddy current power loss  $i^2(t)R$  then varies with square of excitation frequency  $f$ .

- Classical Steinmetz equation for eddy current loss:

$$P_E = K_E f^2 B_{\max}^2 (\text{core volume})$$

- Ferrite core material impedance is capacitive. This causes eddy current power loss to increase as  $f^4$ .

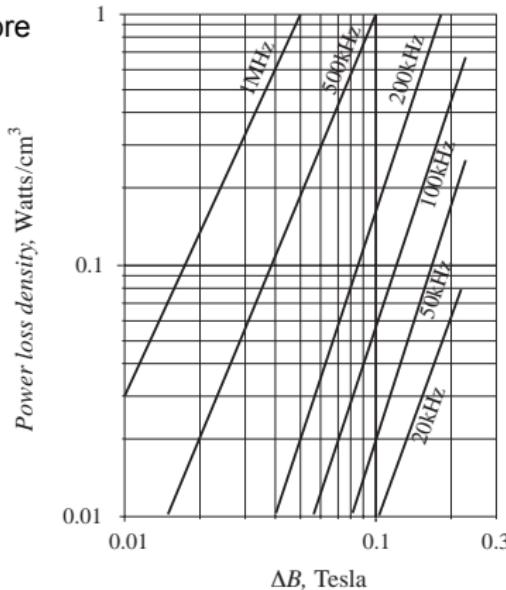

## Total core loss: manufacturer's data

Ferrite core material

Empirical equation, at a fixed frequency:

$$P_{fe} = K_{fe} (\Delta B)^\beta A_c \ell_m$$

# Core materials

| Core type                                         | $B_{sat}$    | Relative core loss | Applications                                    |

|---------------------------------------------------|--------------|--------------------|-------------------------------------------------|

| Laminations<br>iron, silicon steel                | 1.5 - 2.0 T  | high               | 50-60 Hz transformers,<br>inductors             |

| Powdered cores<br>powdered iron,<br>molypermalloy | 0.6 - 0.8 T  | medium             | 1 kHz transformers,<br>100 kHz filter inductors |

| Ferrite<br>Manganese-zinc,<br>Nickel-zinc         | 0.25 - 0.5 T | low                | 20 kHz - 1 MHz<br>transformers,<br>ac inductors |

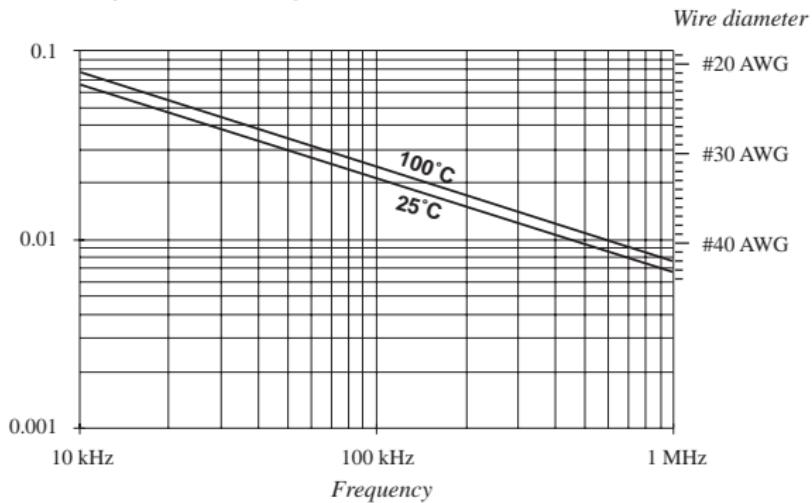

### 13.3.2 Low-frequency copper loss

DC resistance of wire

$$R = \rho \frac{l_b}{A_w}$$

where  $A_w$  is the wire bare cross-sectional area, and  $l_b$  is the length of the wire. The resistivity  $\rho$  is equal to  $1.724 \cdot 10^{-6} \Omega \text{ cm}$  for soft-annealed copper at room temperature. This resistivity increases to  $2.3 \cdot 10^{-6} \Omega \text{ cm}$  at  $100^\circ\text{C}$ .

The wire resistance leads to a power loss of

$$P_{cu} = I_{rms}^2 R$$

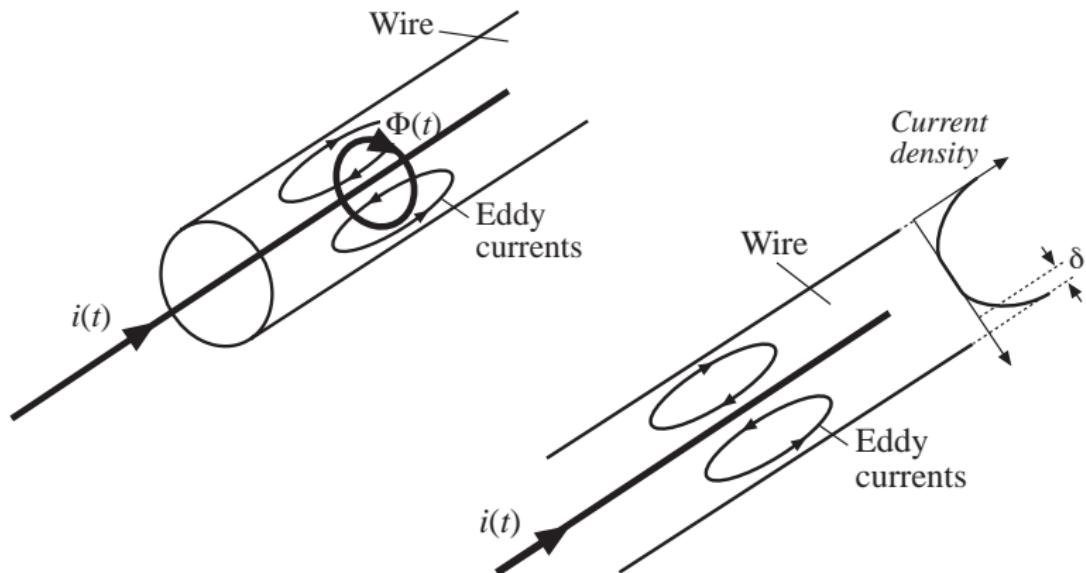

## 13.4 Eddy currents in winding conductors

### 13.4.1 Intro to the skin and proximity effects

# Penetration depth $\delta$

For sinusoidal currents: current density is an exponentially decaying function of distance into the conductor, with characteristic length  $\delta$  known as the *penetration depth* or *skin depth*.

$$\delta = \sqrt{\frac{\rho}{\pi \mu f}}$$

For copper at room temperature:

$$\delta = \frac{7.5}{\sqrt{f}} \text{ cm}$$

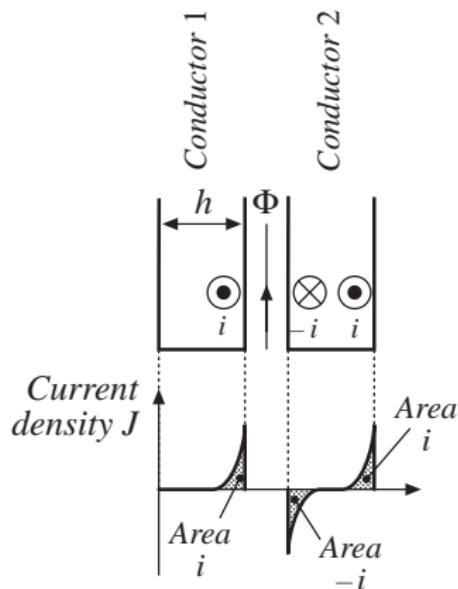

# The proximity effect

Ac current in a conductor induces eddy currents in adjacent conductors by a process called the *proximity effect*. This causes significant power loss in the windings of high-frequency transformers and ac inductors.

A multi-layer foil winding, with  $h \gg \delta$ . Each layer carries net current  $i(t)$ .

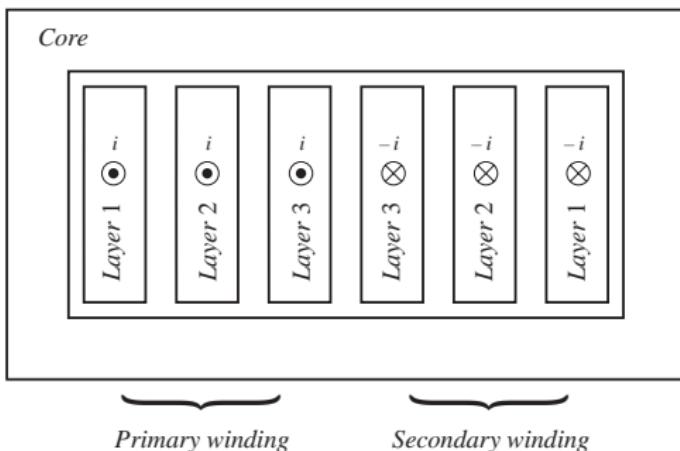

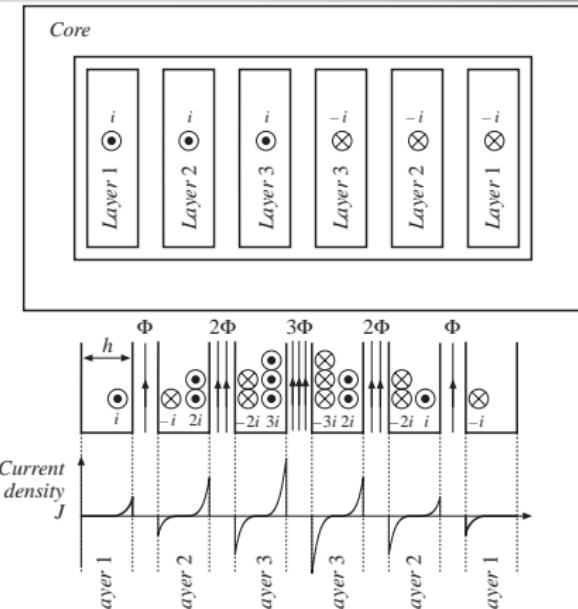

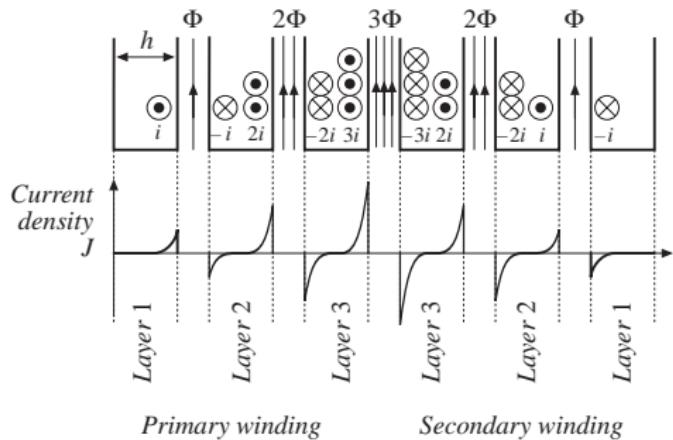

# Example: a two-winding transformer

Cross-sectional view of two-winding transformer example. Primary turns are wound in three layers. For this example, let's assume that each layer is one turn of a flat foil conductor. The secondary is a similar three-layer winding. Each layer carries net current  $i(t)$ . Portions of the windings that lie outside of the core window are not illustrated. Each layer has thickness  $h \gg \delta$ .

# Distribution of currents on surfaces of conductors: two-winding example

Skin effect causes currents to concentrate on surfaces of conductors

Surface current induces equal and opposite current on adjacent conductor

This induced current returns on opposite side of conductor

Net conductor current is equal to  $i(t)$  for each layer, since layers are connected in series

Circulating currents within layers increase with the numbers of layers

## Estimating proximity loss: high-frequency limit

The current  $i(t)$  having rms value  $I$  is confined to thickness  $d$  on the surface of layer 1. Hence the effective “ac” resistance of layer 1 is:

$$R_{ac} = \frac{h}{\delta} R_{dc}$$

This induces copper loss  $P_1$  in layer 1:

$$P_1 = I^2 R_{ac}$$

Power loss  $P_2$  in layer 2 is:

$$P_2 = P_1 + 4P_1 = 5P_1$$

Power loss  $P_3$  in layer 3 is:

$$P_3 = (2^2 + 3^2)P_1 = 13P_1$$

Power loss  $P_m$  in layer  $m$  is:

$$P_m = I^2 \left[ (m-1)^2 + m^2 \right] \left( \frac{h}{\delta} R_{dc} \right)$$

## Total loss in $M$ -layer winding: high-frequency limit

Add up losses in each layer:

$$\begin{aligned} P &= I^2 \left( \frac{h}{\delta} R_{dc} \right) \sum_{m=1}^M \left[ (m-1)^2 + m^2 \right] \\ &= I^2 \left( \frac{h}{\delta} R_{dc} \right) \frac{M}{3} (2M^2 + 1) \end{aligned}$$

**Compare with dc copper loss:**

If foil thickness were  $H = \delta$ , then at dc each layer would produce copper loss  $P_L$ . The copper loss of the  $M$ -layer winding would be

$$P_{dc} = I^2 M R_{dc}$$

So the proximity effect increases the copper loss by a factor of

$$F_R = \frac{P}{P_{dc}} = \frac{1}{3} \left( \frac{h}{\delta} \right) (2M^2 + 1)$$

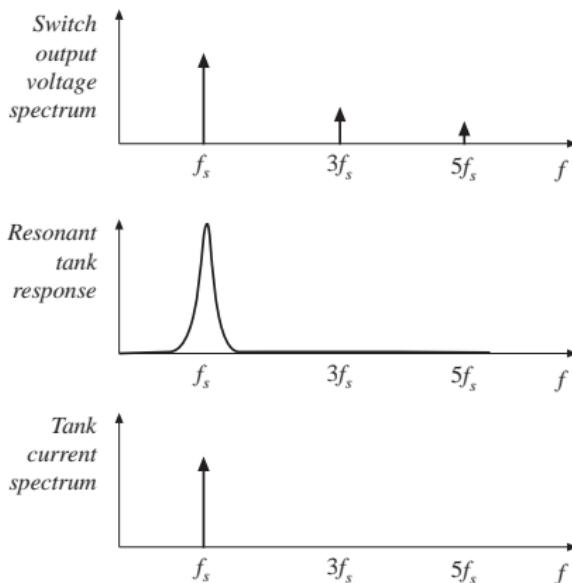

# Discussion: design of winding geometry to minimize proximity loss

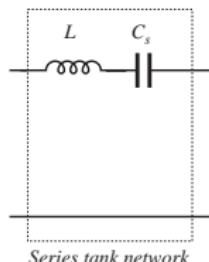

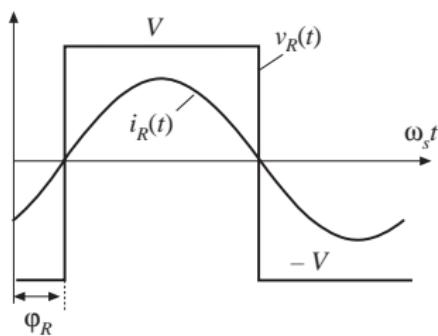

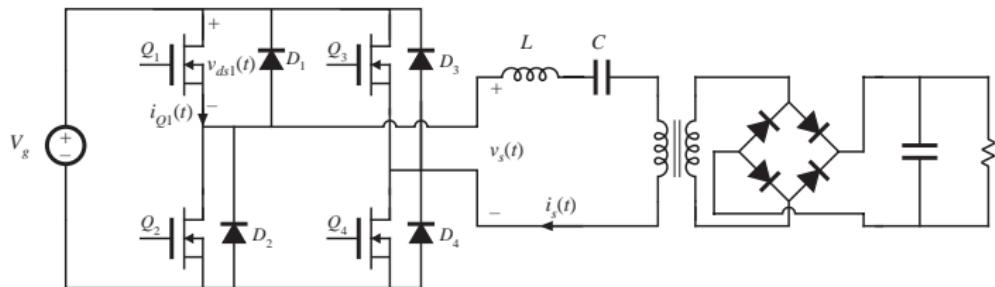

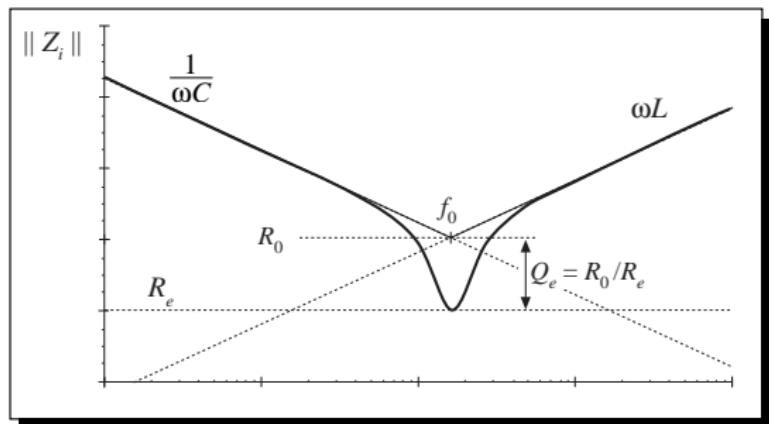

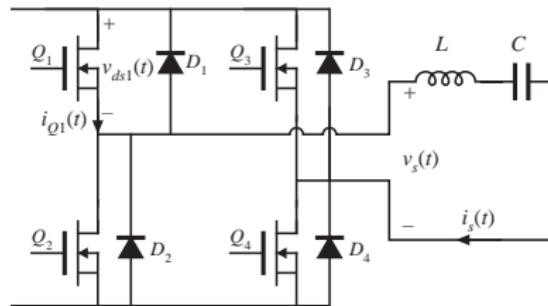

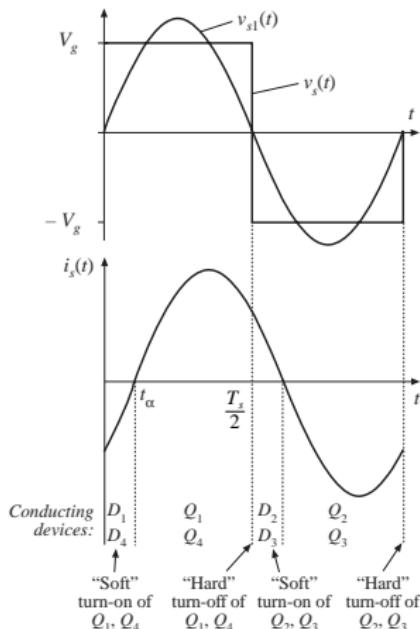

---