# Computation structures Tutorial 4: µ-code for ULg03

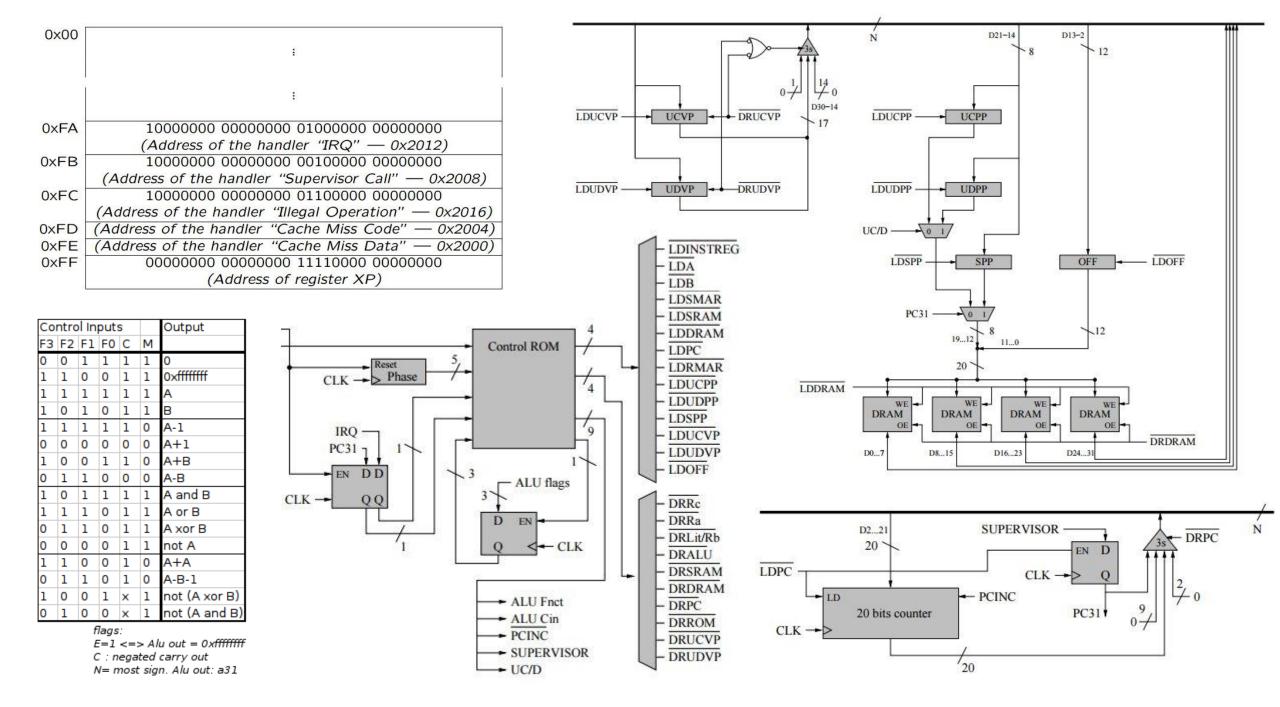

#### ULg02 - constant ROM and XP register

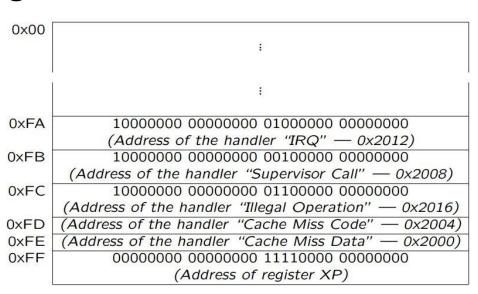

- For handling exceptions, ULg02 introduces the XP (R30) register in which is stored the user program address at which the execution must return after the system have finished executed an exception handler.

- ULg02 introduces a control ROM storing useful constants:

- Address of XP

- Address of exception handlers

#### ULg03, introducing virtual memory

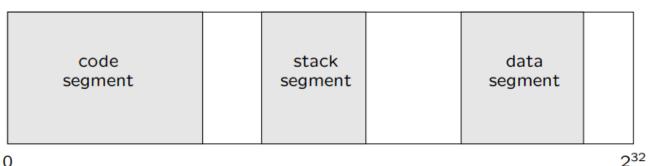

• Virtual memory: user programs have virtually access to a large contiguous space of dynamic memory (larger than the actual amount of available physical memory). In practice, the memory is fragmented into pages which can be stored on disk.

#### • Goal:

- Make it easier to have several processes

- A process cannot mess with the memory of other processes, nor the system memory

- More memory available than actual amount of available physical memory

- No need for reserving a fixed amount of memory for processes execution

#### Virtual memory – how it works

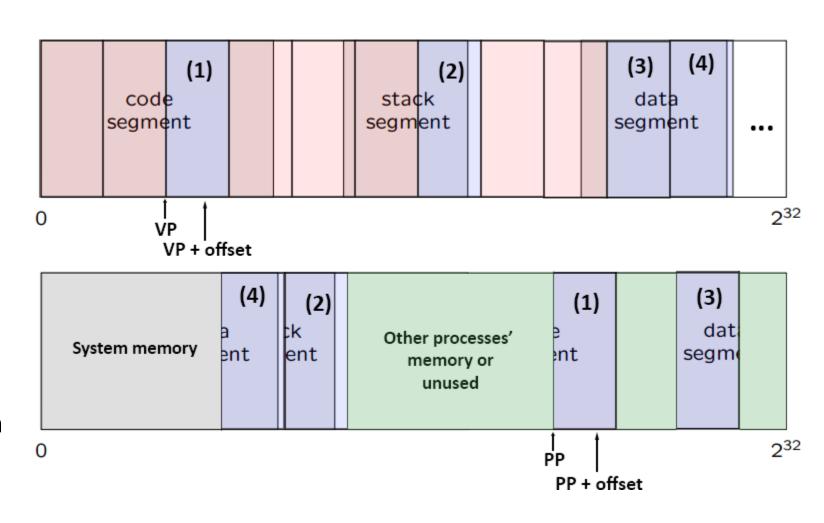

Virtual memory view of a user program

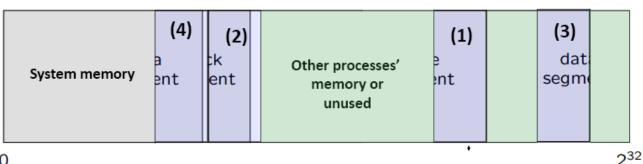

System operates in physical memory

User programs operate in virtual memory

Splitted in pages

A **page** is a fixed-size set of contiguous memory locations that can contain anything (code, stack, data,...)

Physical (actual) memory

Useful pages are stored in memory while other can be stored on disk ⇒ virtually more memory available than actual physical memory

(

#### Virtual memory – how it works

- Virtual address: an address in the virtual space

- Physical address: the address in the actual memory

- All addresses have two components:

- Page address: VP (virtual page) or PP/SP (physical page/system page)

- Offset: the address offset in the page

### Virtual memory – page table

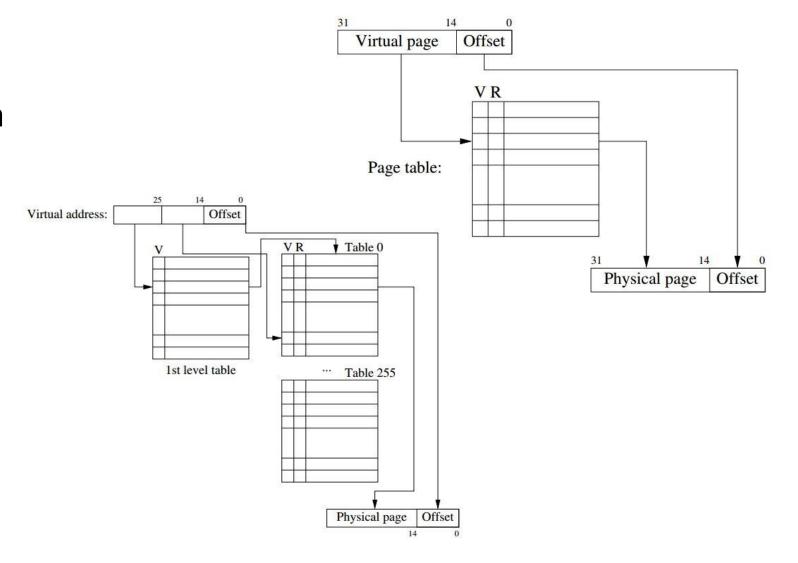

- The system translates virtual pages (VP) into physical pages (PP) using a page table

- The page table is stored in the system memory

- Sometimes uses a twolevel table for storage efficiency

- Need to access memory for translating virtual addresses ⇒ very inefficient

## Virtual memory – optimize look-up with caching

- Locality principle: accesses that are time-wise close are often address-wise close

- We can store PP, the result of the last translation of VP, in a register because the next translation will probably yield the same PP!

- Frequent memory accesses:

- Code access: instructions

- Data access: actual data or stack

- Both types of accesses are cached

## Virtual memory – optimize look-up with caching

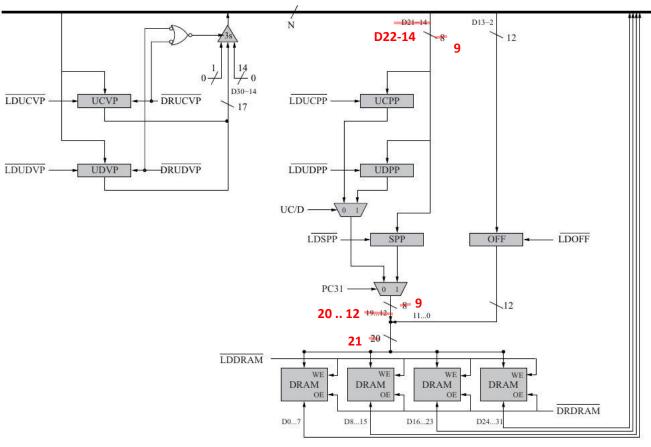

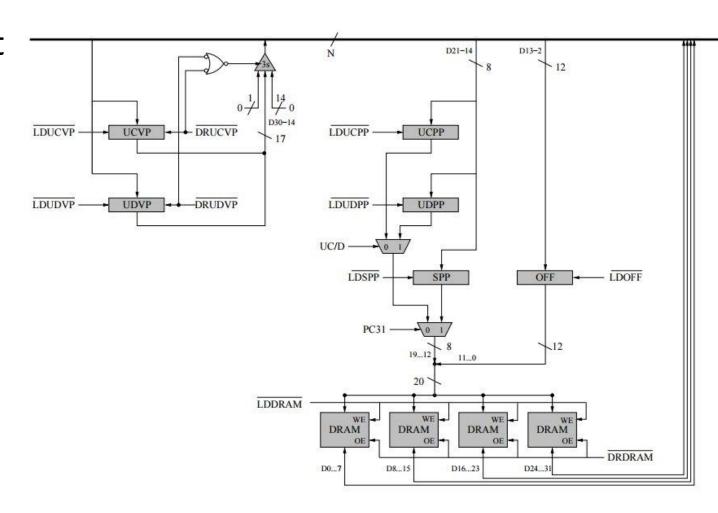

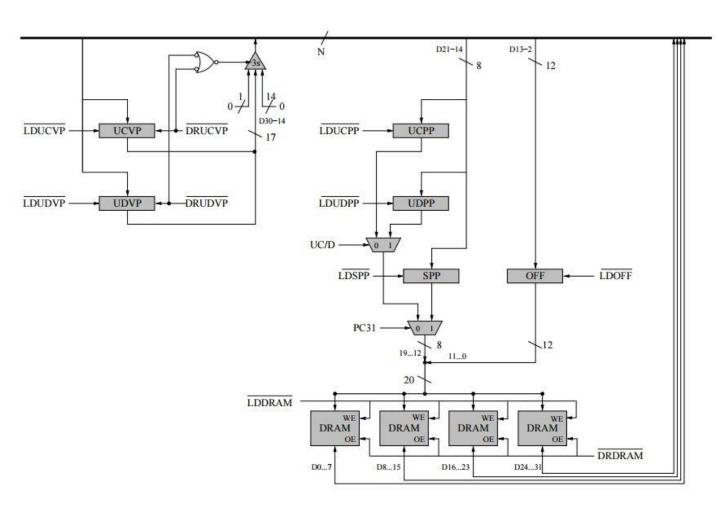

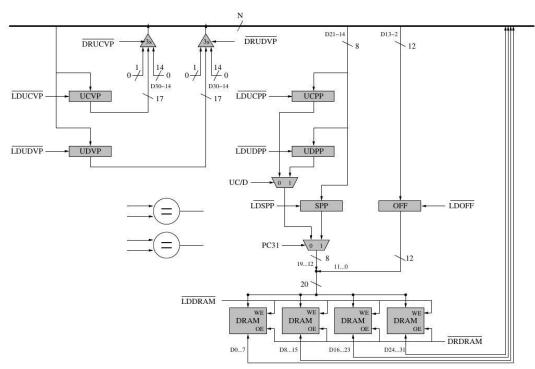

- In user mode:

- U\*VP and U\*PP contains respectively virtual page address and translated physical address

- Code: UCVP and UCPP

- Data: UDVP and UDPP

- UC/D is a flag allowing to choose the cache among those two

- In SVR mode (PC31 = 1), uses physical memory:

- SPP: System Physical Page

- In both cases, the offset is stored in register OFF

#### Virtual memory – cache hit and miss

- Cache hit: if the cache register contains the expected address.

- Cache miss: if the cache register doesn't contain the expected address.

- Cache miss triggers a « Cache miss code » or a « Cache miss data » **exception** that is handled at the  $\mu$ -code level.

- The handlers of those exceptions update the corresponding cache with the expected address

#### Virtual memory – a cache miss data handler

XP – 4 for re-executing the interrupted instruction (only for cache miss data, not for cache miss code) SUBC(XP, 4, XP) plan to reexecute the instruction h\_stub: that has been suspended ST(r0, User, r31) save ST(r1, User+4, r31) ST(r30, User+30\*4)CMOVE(KStack, SP) | Load the system SP RDUDVP(r1) the virtual page address to be translated pass it as argument PUSH(r1) BR(CMHandler,LP) | call the Handler remove the argument from the stack DEALLOCATE(1) Update physical page address UDPP WRUDPP(r0) install the returned value LD(r31, User, r0) restore LD(r31, User+4, r1) LD(r31, User+30\*4, r30) JMP(XP) | return to application Go back to the interrupted instruction (of

Go back to the interrupted instruction (of which the address is stored in XP)

#### Exercise 2 - January 2017

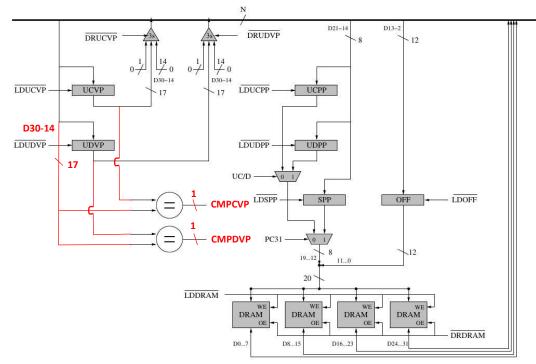

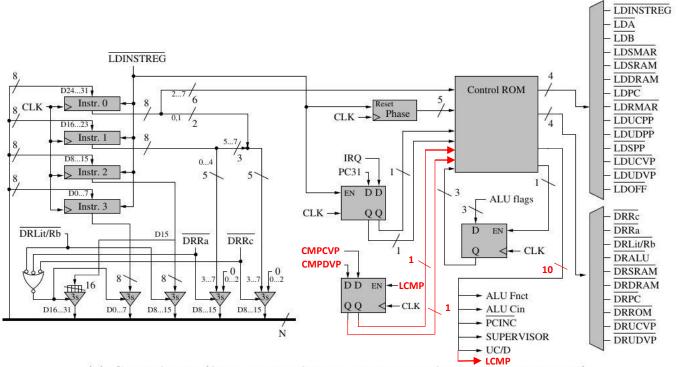

(b) Virtual RAM (hint: notice the new unconnected comparators and the new output wiring of UCVP and UDVP, which are no longer 3 state)

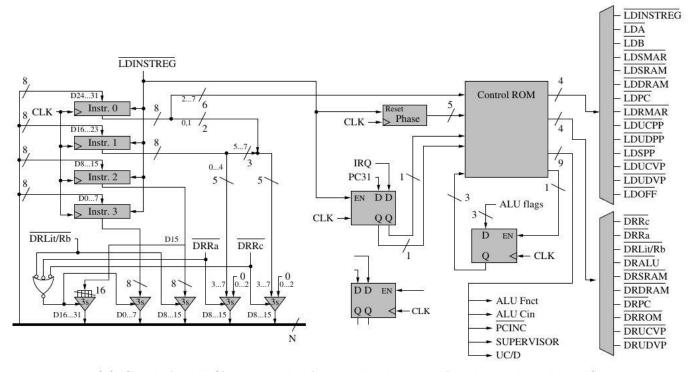

(a) Control unit (hint: notice the new unconnected memory component)

## Exercise 2(a) - January 2017

(b) Virtual RAM (hint: notice the new unconnected comparators and the new output wiring of UCVP and UDVP, which are no longer 3 state)

(a) Control unit (hint: notice the new unconnected memory component)

#### Exercise 2(a) - January 2017

Optimized (with hardware comparison)

| Cond         | ALU           | DR   | LD      | Sig     | 300  |

|--------------|---------------|------|---------|---------|------|

| F7-0-0000000 | 30.000        | Ra   | SMAR    | 1719048 | 100  |

|              | amoracana ana | SRAM | Α       | LCMP    | 8    |

| CMPDVP = 0   | Oxffffffff    | ALU  | A       |         | 1    |

|              | А             | ALU  | RMAR    |         | 8    |

|              |               | ROM  | SMAR    |         | 3    |

|              |               | PC   | SRAM    |         | 3    |

|              | A-1           | ALU  | RMAR    |         | 8    |

|              | 100           | ROM  | PC      | SVR     | 8    |

|              |               | PC   | SPP     |         | 3    |

|              |               | PC   | OFF     | PC+     | 8    |

|              |               | DRAM | INSTREG |         | 1    |

| CMPDVP = 1   | А             | ALU  | OFF     |         | 8    |

|              |               | DRAM | В       | UC/D    | 100  |

|              |               | Rb   | SMAR    |         | 8    |

|              |               | SRAM | A       |         | 8    |

|              |               | Rc   | SMAR    |         | 100  |

|              | A-B           | ALU  | A       | LF      | 8    |

| N = 0        | 0             | ALU  | SRAM    |         | 3    |

| N = 1        | В             | ALU  | SRAM    |         | 8    |

|              | А             | ALU  | A       |         | 2000 |

|              |               | PC   | OFF     | LCMP    | 1    |

| CMPCVP = 0   | Oxffffffff    | ALU  | A       |         | 1    |

|              | A             | ALU  | RMAR    |         | 1    |

|              |               | ROM  | SMAR    |         | 1    |

|              |               | PC   | SRAM    |         | 1    |

|              | A-1           | ALU  | A       |         | 1    |

|              | A-1           | ALU  | RMAR    |         | 1    |

|              |               | ROM  | PC      | SVR     | 1    |

|              |               | PC   | SPP     |         | 1    |

|              |               | PC   | OFF     | PC+     | 1    |

|              |               | DRAM | INSTREG |         | 2    |

| CMPCVP = 1   |               | DRAM | INSTREG | PC+     | 1    |

Basic (without hardware comparison)

| Cona  | ALU        | DK   | LD                 | Sig       |

|-------|------------|------|--------------------|-----------|

|       | 200000     | UDVP | A                  |           |

|       |            | Ra   | SMAR               |           |

|       |            | SRAM | OFF                |           |

|       |            | SRAM | UDVP               |           |

|       |            | UDVP | В                  |           |

|       | !(A^B)     | ALU  | Α                  | LF        |

| E = 0 | Oxffffffff | ALU  | А                  |           |

|       | A          | ALU  | RMAR               |           |

|       | 28         | ROM  | SMAR               |           |

|       |            | PC   | SRAM               |           |

|       | A - 1      | ALU  | RMAR               |           |

|       | 13.5.7     | ROM  | PC                 | SVR       |

|       |            | PC   | SPP                | J.,,,     |

|       |            | PC   | OFF                | PC+       |

|       |            | DRAM | INSTREG            |           |

| E = 1 |            |      |                    |           |

| C = 1 | A          |      |                    |           |

|       |            | ALU  |                    |           |

|       | A          | ALU  | A                  |           |

|       | A          | ALU  | A                  |           |

|       |            | DRAM | В                  | UC/D      |

|       |            | Rb   | SMAR               |           |

|       |            | SRAM | A                  |           |

|       |            | Rc   | SMAR               |           |

|       | A-B        |      | A                  | LF        |

| N = 0 | 0          | ALU  |                    |           |

| N = 1 | В          | ALU  | SRAM               |           |

|       |            | UCVP | Α                  |           |

|       |            | PC   | OFF                |           |

|       |            | PC   | UCVP               |           |

|       |            | UCVP | В                  |           |

|       | !(A ^ B)   | ALU  | Α                  | LF        |

| E = 0 | 0xffffffff | ALU  | А                  |           |

|       | A          | ALU  | RMAR               |           |

|       | 100        | ROM  | SMAR               |           |

|       |            | PC   | SRAM               |           |

|       | A-1        | ALU  | A                  |           |

|       | A-1        | ALU  | RMAR               |           |

|       |            | ROM  | PC                 | SVR       |

|       |            | PC   | SPP                | - * * * * |

|       |            | PC   | OFF                | PC+       |

|       |            | DRAM | 7.00               | 107       |

| E = 1 |            | DRAM | INSTREG<br>INSTREG | PC+       |

- Optimized version almost two times faster when there is no cache miss (11 phases instead of 21)

- Notice the padding in the basic version (not necessary in optimized version as we use different memory components for the flags)

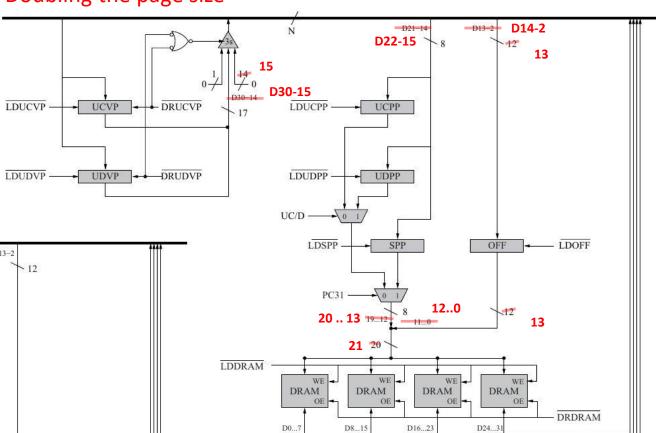

#### Exercise 3

#### Doubling the page size

#### Doubling the number of pages